PCIe Analyzers

State-of-the-Art Protocol Analyzers for PCI Express 5.0, 4.0, 3.0

Over the past two decades, PCI Express (PCIe) has become the de-facto high speed serial bus architecture. VIAVI has developed a suite of advanced PCIe analyzers to support the widespread adoption of PCIe and ensure system and component conformance to industry standards.

As a contributing member of the Peripheral Component Interconnect Special Interest Group (PCI-SIG), VIAVI has directly influenced the innovative test practices and specifications that enable the high bandwidth performance and reliability of PCI Express.

Productos

-

Xgig 5P16 Analyzer/Exerciser/Jammer Platform for PCI Express 5.0

Combines A/E/J functionality on the same platform with support for the latest PCIe, NVMe and CXL specifications, and...

-

Xgig 5P8 Analyzer/Exerciser/Jammer Platform for PCI Express 5.0

Provides full-speed 32Gbps data capture, enabling detailed functional and performance analysis of PCIe protocol...

-

Xgig 4K16 Analyzer/Jammer Platform for PCI Express 4.0

The most powerful PCIe Gen 4.0 analysis system available, offering complete visibility into traffic flows with...

-

Xgig Exerciser Host Test Stand Interposer Module for PCI Express 5.0

The PCIe Exerciser Host Test Stand provides connectivity and power to a PCIe adapter card endpoint for testing and...

-

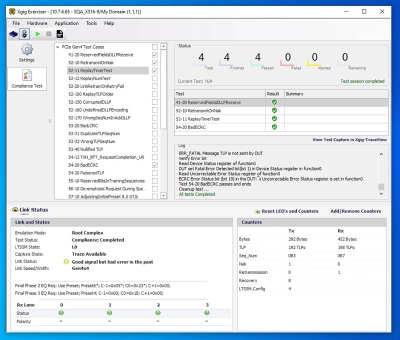

Xgig Exerciser for PCI Express 5.0

The PCIe Exerciser generates PCIe data streams and responses for compliance testing and analysis PCIe 5.0 protocol...

What is a PCIe Analyzer?

Peripheral Component Interconnect Express (PCIe) is the industry standard computer bus architecture. PCIe was first introduced in 2002 as a successor to PCI and Accelerated Graphics Port (AGP) interfaces for internal computer connections and is now approaching its 6th successful generation. PCIe uses a point-to-point topology to provide separate high-speed links to each connected device.

Specifications for PCIe serial expansion buses and related components are defined by the Peripheral Component Interconnect Special Interest Group (PCI-SIG), an industry consortium that owns and maintains all PCI and PCIe standards.

A PCIe analyzer is a powerful test solution used to capture and interpret data packets transferred via a PCIe interface. Data is converted into useful protocol decodes to assess conformance to relevant PCI-SIG specifications. Any logical errors are detected and characterized.

An advanced PCI Express protocol analyzer might also include exerciser or jammer functionality on the same platform. This enables more cost-effective and robust PCIe testing and development with less set up time.

What PCIe Versions are Available for VIAVI PCIe Analyzers?

PCI Express has maintained a lofty standard of bandwidth and speed doubling with each successive release, along with downward compatibility among all versions. Developers and manufacturers have continued to meet these targets, despite mounting technical challenges with signal loss, crosstalk, and latency.

Versatile, user-friendly VIAVI PCIe analyzers have adapted to these changes. Improved features, memory, and automation have been incorporated to keep pace with new and emerging PCIe technologies.

- High PCIe 5.0 bandwidth requirements, along with new equalization bypass and precoding options performed at PCIe 5.0 speeds, have complicated hardware and system testing. The VIAVI Xgig Analyzer family supports robust PCI Express 5.0 slot testing and protocol analysis with superior computing, memory, and segmentation capabilities. Decoding of Compute Express Link (CXL) and other alternate protocol traffic is also supported.

- PCIe 5.0 has achieved an impressive 64 GB/sec of throughput in each direction without significant functional changes to the link or transaction layers. Physical layer upgrades included more advanced EIEOS ordered sets and equalization sequences to improve signal integrity and reduce latency. PCIe 5.0 also supports alternate protocols through updated TS1 and TS2 training sequences.

- The VIAVI Xgig 5P16 Analyzer/Exerciser/Jammer Platform for PCIe 5 is an integrated system that allows Analyzer, Exerciser and Jammer functionality on the same platform enabling users to cost-effectively configure equipment to best meet their individual and specific requirements. Similarly, the Xgig 5P8 Analyzer/Jammer Platform for PCI Express 5.0 platform provides protocol analysis for PCIe 5th generation traffic at all layers of the stack. It supports link widths up-to 8-lanes.

- PCIe 4.0 was developed with the high bandwidth applications which emerged during the long PCIe 3.0 lifecycle in mind. The PCIe 4.0 specification also incorporated variable lane widths and new lane margining features to improve reliability.

- The VIAVI Xgig 4K16 PCI Express 4.0 Protocol Analyzer/Jammer is a comprehensive solution for version 4.0 protocol analysis and error injection, as well as NVMe testing and development applications. Simultaneous protocol analysis and jamming can be performed with a single interposer. Memory segmentation is used to capture data from multiple traces. The Xgig 4K4 Analyzer Platform for PCI Express 4.0 offers similar performance, but with link widths to 4-lanes.

|

PCIe Version |

Release Year |

Transfer Rate |

Throughput/Lane |

x16 Throughput |

|---|---|---|---|---|

|

1.0 |

2003 |

2.5 GT/sec |

250 MB/sec |

4.0 GB/sec |

|

2.0 |

2007 |

5.0 GT/sec |

500 MB/sec |

8.0 GB/sec |

|

3.0 |

2010 |

8.0 GT/sec |

1.0 GB/sec |

16.0 GB/sec |

|

4.0 |

2017 |

16.0 GT/sec |

2.0 GB/sec |

32.0 GB/sec |

|

5.0 |

2019 |

32.0 GT/sec |

4.0 GB/sec |

64.0 GB/sec |

How Do You Use a PCIe Analyzer?

A PCI Express protocol analyzer is comprised of both hardware and software components. Hardware is required to physically connect the protocol analyzer to the link under test so that data can be collected without disruption. Once this connection is established, the software components of the PCIe analyzer are used to validate the link and diagnose any errors encountered.

- Protocol Analysis

The primary function of a PCIe protocol analyzer is to check PCI Express performance versus the relevant PCI-SIG protocol. Software test settings allow recording, storage, and traffic filtering preferences of the test to be configured. Xgig expert software can efficiently sort through millions of events to determine physical, upper, and logical layer conformance to PCIe protocols. Errors, interoperability issues, and performance problems are quickly identified. - Jamming

The hardware connection established for protocol analysis can also be used to actively inject errors into the PCIe link. Intelligent, protocol aware jamming capabilities can be used to simulate real world or worst case (corner) conditions. Jamming capabilities also allow the effectiveness of the error recovery process to be evaluated. - Troubleshooting

A PCI Express check performed by a PCIe analyzer can be leveraged as an effective debugging tool. Transaction testing and recording for multiple traces provides a solid foundation for debugging applications. Advanced debug features, error reporting, and trigger and search capabilities also minimize diagnosis time in development or real-world scenarios.

What Does a PCIe Analyzer Test/Measure?

The best PCI Express analyzers are capable of measuring and testing a wide variety of outputs to fully assess PCIe performance.

- Link Bring-Up or training issues, such as incorrect speeds or poor signal integrity, can be diagnosed with a PCIe analyzer. Once the L0 state of normal operation is reached, performance problems like excessive replays and error recoveries can be discovered and measured through post capture analysis.

- PHY Layer Mismatches between the transmitting (Tx) and receiving (Rx) logic are a common problem that can prolong the exit state from electrical idle (EI). A PCIe analyzer with short lock times can be used to quickly identify these issues. Capturing and analyzing transaction data during low power states can prevent misalignments that contribute to latency.

- Real-Time Metrics are more actionable with per-lane resolution and full-speed data capture. Non-acknowledgements, pending I/O transactions, replays, and transaction queue depths are among the metrics than can shed more light on link performance and potential problems. Xgig expert software can quickly organize these metrics into detailed, customizable reports.

Why Do You Need to Analyze the PCIe Protocol?

VIAVI is among the proud member organizations of PCI-SIG providing valuable input into new specifications and testing standards. The standardization and acceptance of PCIe protocols has led to greater interoperability between vendors and components, and improved reliability.

- PCIe features and innovations include downward compatibility, autonomous power management, and ease of expandability. These well received benefits have fostered widespread industry adoption of PCIe. Compliance workshops, developer conferences, and interoperability test sessions are continually sponsored by PCI-SIG. These events leverage the popularity of PCIe to promote commonality in protocol testing among vendors.

- Locating and decoding protocol information using a PCI bus analyzer establishes more than just protocol compliance. As a byproduct of physical layer protocol testing, a PCIe analyzer also determines how successfully data transfer is performed over a given link. Errors that might have resulted in field performance issues can be fully characterized and addressed prior to product release.

- Alternatives to PCIe protocol testing can be completed with traditional test tools like oscilloscopes. These options become more time consuming with each successive PCIe release. An advanced PCI Express protocol analyzer with direct visibility into inline traffic is much more efficient and informative than indirect measurement of endpoint performance.

PCIe Analyzer Features to Look for Before Investing

PCI Express protocol analyzer feature sets have expanded along with the bandwidth and complexity of each new release. Innovative PCIe analyzers provide a high return on investment by improving test efficiency and versatility.

- Downward compatibility is an essential PCIe protocol analyzer feature, with the release cadence for new PCIe iterations planned at two-year intervals. The best PCIe analyzers can accommodate link widths from 1-16 lanes and data rates ranging from 2.5 to 32 GT/sec (for PCIe 5.0).

- Memory size and segmentation for the capture of either long traces or multiple traces allows you to test PCI Express slot performance with more granularity and diagnostic prowess. Captured data can be recalled by the PCI Express analyzer to pinpoint the physical source of errors or defects.

- NVMe protocol test capabilities compliment the PCI Express check with traffic flow visibility for the non-volatile-memory counterpart of PCIe. VIAVI protocol analyzers include NVMe trigger and search traffic functions along with NVMe decoding at all layers of the stack.

- Interposer autotuning reduces test time by automatically detecting and adjusting for the correct PCIe parameters during test setup. Autotuning capabilities also improve the overall reliability and repeatability of the PCIe bus analyzer test.

- Remote debugging is intended to address the rapid propagation of PCIe throughout the network computing landscape. Host-client connectivity features of PCI bus analyzers allow Ethernet connections to be leveraged for remote error monitoring and diagnosis.

- Jammer and exerciser functionality within a PCIe analyzer enables the same hardware to perform multiple test processes efficiently. The deep packet inspection of the protocol analyzer is complimented by the inline error injection of the jammer to test recovery times. Exerciser features can be used to emulate traffic and/or linked devices and test component compliance.

Asistencia en cada paso

Proporcionamos soporte técnico, servicios, una formación completa y los recursos que necesita. Todo ello forma parte de lo que hacemos con el fin de maximizar el valor de su inversión en VIAVI.

Pregunte a un experto

Póngase en contacto con nosotros para obtener más información o recibir un presupuesto. Contamos con expertos que podrán proporcionarle las respuestas adecuadas a cualquier pregunta que le surja.