PCIe 4.0

Des technologies d’analyse et de brouillage avancées avec une intégrité du signal de pointe et des capacités d’auto-ajustement

Produits

-

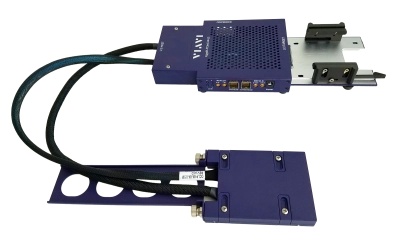

Xgig 4K16 Analyzer/Jammer Platform for PCI Express 4.0

The most powerful PCIe Gen 4.0 analysis system available, offering complete visibility into traffic flows with...

-

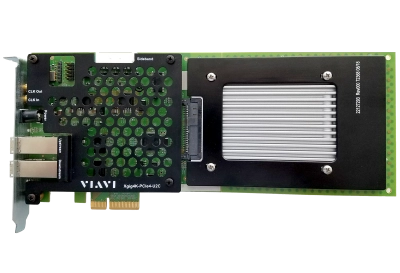

Xgig 4K4 Analyzer Platform for PCI Express 4.0

The Xgig 4K4 platform provides protocol analysis for PCIe and NVMe traffic at all layers of the stack

-

Xgig E1 EDSFF Interposer Module for PCI Express 4.0

Xgig4K-PCIe4-X8-E1 is an Active Interposer optimized for developing, debugging and performance tuning NVMe SSD...

-

Xgig CEM Type-B, 16-lane Interposer Module for PCI Express 4.0

The PCIe 4.0 16-lane CEM Type-B Interposer enables debug and verification of new ICs, new system hardware designs,...

-

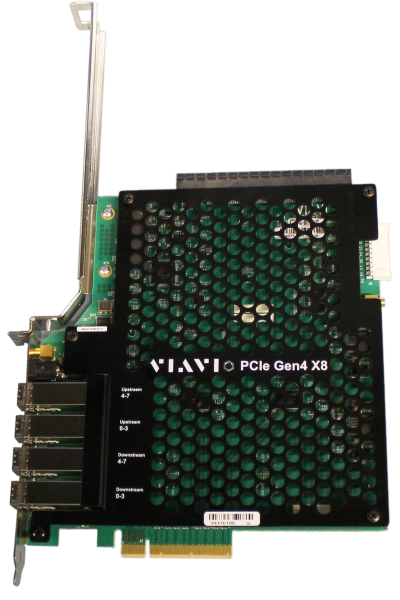

Xgig CEM, 8-lane Interposer Module for PCI Express 4.0

The PCIe4, 8-lane CEM-slot Interposer enables debug and verification of new ICs, system hardware designs, FPGA...

-

Xgig CEM-slot, 4-lane Interposer Module for PCI Express 4.0

The PCIe4, 4-lane CEM-slot Interposer enables debug and verification of new ICs, system hardware designs, FPGA...

-

Xgig U.3-Server, 4-lane Interposer Module for PCI Express 4.0

Provides a tap of communication between a host-system and a U.3 NVMe SSD for input to the VIAVI PCIe 4.0 Analyzer...

-

Xgig U.2B-Server, 4-lane Interposer Module for PCI Express 4.0

This U.2-Server, version B Interposer is optimized for development, debugging and tuning of NVMe SSD operation in...

-

Xgig U.2-CEM, 4-lane Interposer Module for PCI Express 4.0

This U.2-CEM Interposer is optimized for NVMe SSD development enabling debug and analysis

-

Xgig M.2, 4-lane Interposer Module for PCI Express 4.0

The M.2, 4-lane Interposer for PCI Express® 4.0 is an Active Interposer with a design optimized for M.2 SSD...

-

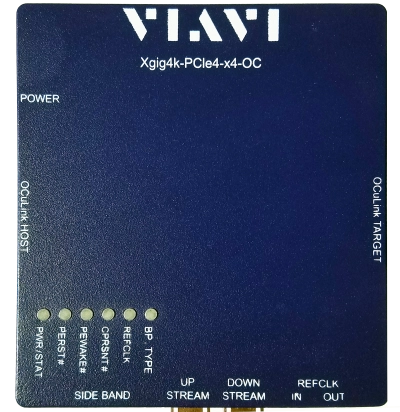

Xgig Oculink, 4-lane Interposer Module for PCI Express 4.0

The PCIe4, 4-lane OCulink/Slimline Interposer enables debug of new ICs, hardware designs, FPGA firmware, system BIOS...

-

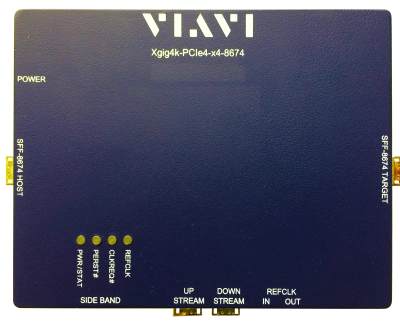

Xgig SFF-8674, 4-lane Interposer Module for PCI Express 4.0

The SFF-8674 Interposer enables protocol analysis of PCI Express 4.0 traffic between an SFF-8674 attached host...

-

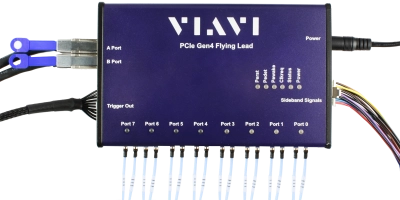

Xgig Flying-Lead, 4-lane Interposer Module for PCI Express 4.0

The Xgig Flying-Lead Interposer captures signals between controller ICs on the same PCB where there is no connector...

-

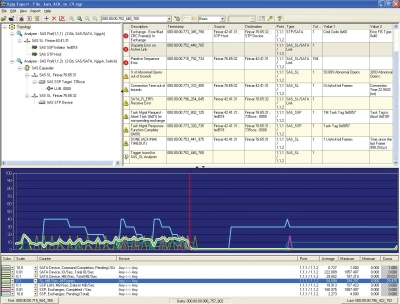

Xgig Expert

Expert software comes standard with all Xgig Analyzers to provide a unique and robust set of debugging and analysis...

-

Xgig Jammer for PCI Express 5.0

The Xgig® Jammer manipulates live network traffic to simulate errors in real time, enabling users to verify the...

-

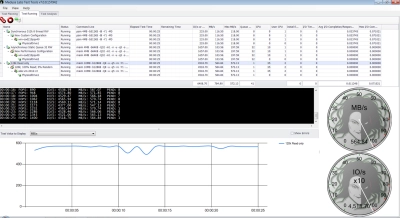

Medusa Labs Test Tools Suite

Medusa Labs Test Tools Suite is the leading application-based data testing and signal integrity testing tool...

Qu’est-ce que le PCIe 4.0 ?

Le PCIe 4.0 (parfois également appelé PCIe 4, PCIe Gen 4, PCI 4 ou PCI Express 4.0) est la quatrième génération de norme d’interconnexion expresse de composants périphériques (PCIe), une technologie de bus informatique haut débit. À ceux qui se demandent « si le PCIe 4.0 est rétrocompatible », nous répondons qu’il est conçu pour prendre en charge les applications exigeant une bande passante plus élevée à un prix moindre tout en conservant une compatibilité complète avec les générations de PCIe antérieures.

Cette spécification, qui définit des largeurs de voies variables (x1, x2, x4, x8, x16 et x32) permettant aux développeurs d’accéder à de nombreuses largeurs de voies et configurations de débit, est adaptée à des applications aux exigences variées en matière de bande passante. Ainsi, les applications de stockage utilisent les largeurs de voie PCIe x4, tandis que les applications de haute performance exploitant des bandes passantes augmentées peuvent utiliser les largeurs de voie PCIe x16.

Une carte mère compatible PCIe 4.0 couplée avec un SSD PCIe 4.0 peut produire des débits de lecture/écriture séquentiels deux fois plus rapides que la gamme de SSD PCIe 3.0 (la génération précédente) et plus de dix fois plus rapides que la technologie de disque SSD SATA.

La spécification PCI Express 4.0 a été finalisée en octobre 2017 avec un taux de transfert (de bits) annoncé de 16 GT/s, ce qui représente le double de la version précédente, le PCIe 3.0. Le tableau ci-dessous présente les options de bande passante agrégée offertes par le PCIe 3.0 et, en comparaison, par le PCIe 4.0.

| Bande passante en Gbit/s | PCIE X1 | PCIE X2 | PCIE X4 | PCIE X8 | PCIE X16 |

|---|---|---|---|---|---|

| PCIe 3.0 | 1,97 | 3,94 | 7,87 | 15,75 | 31,51 |

| PCIe 4.0 | 3,94 | 7,87 | 15,75 | 31,51 | 63,02 |

En quoi le PCIe 4.0 est-il différent ?

En 2003 sortait la première génération de PCI Express, le PCIe 1.0, qui allait rapidement remplacer les normes de bus qui la précédaient directement, le PCI et l’AGP (Accelerated Graphics Port). Cette dernière avait été spécifiquement développée pour les connexions de contrôleurs graphiques ayant des besoins supérieurs en bande passante.

Les améliorations par rapport au PCI étaient immédiatement visibles, avec un format d’interface série remplaçant le format parallèle du PCI et des bus individuels pour chaque appareil connecté remplaçant la lourde architecture de bus partagé du PCI. Le PCIe 1.0, initialement appelé Interconnexion à haut débit, offrait une spécification de bande passante de 250 Mo/s par voie et un taux de transfert de 2,5 GT/s.

La convention de doublement de la bande passante à chaque nouvelle version de la norme PCIe a été mise en place avec les versions 2.0 et 3.0, sorties respectivement en 2007 et en 2010. Les améliorations progressives apportées au PCIe 3.0 incluaient un procédé d’encodage mis à niveau et passant de 8b/10b à 128b/130b. À chaque nouvelle version, la norme PCIe est demeurée compatible avec les versions précédentes, bien que la version et le débit les plus faibles entre le port PCIe et la carte de connexion dictent toujours la performance et les contraintes réelles de la bande passante en termes de performance et de durée.

Rompant avec la fréquence de sortie habituelle de quatre ans entre les versions qui l’avaient précédée, l’arrivée de la spécification PCIe 4.0 finale a demandé sept années complètes après le PCIe 3.0. En ce qui concerne le PCIe 4.0, les développeurs ont eu plus de difficultés à conserver la norme établie de doublement de la bande passante avec un facteur de forme mécanique et électrique compatible avec les versions précédentes caractérisant le PCIe.

Tout en répondant à cette attente difficile en matière de performance, le PCIe Gen4 a également apporté des améliorations fonctionnelles, notamment une réduction de la latence du système, l’évolutivité des voies de bande passante ajoutées et des fonctions de mise en marge de voies afin dévaluer l’intégrité et la fiabilité électriques pour chaque voie du canal PCIe.

Débit du PCIe Gen 4

En plus de nombreuses améliorations supplémentaires, le PCIe Gen4 se caractérise principalement par un renforcement notable du débit qui demeure son atout principal et autour duquel de nombreux avantages et possibilités se sont ajoutés au bénéfice de nouvelles applications. L’amélioration progressive du débit avec chaque nouvelle version a aujourd’hui amené le PCIe x4 (quatre voies) à un niveau surpassant le débit de la première génération de PCIe x16 (seize voies).

Afin de fournir un exemple concret, le taux de transfert pour la norme PCIe 4.0 correspond à une commutation de tension sur une paire différentielle intervenant 16 millions de fois par seconde.

Cette tradition de doublement du débit du PCIe a permis au PCIe 4.0 d’engendrer des économies pour les applications de pointe telles que les serveurs de cloud et les datacenters, tout en améliorant la performance, l’expérience utilisateur et les économies immobilières des appareils autonomes tels que les ordinateurs portables et les tablettes.

Malgré l’augmentation exceptionnelle en matière de spécifications de débit binaire et de bande passante réalisée ces 16 dernières années, un débit plus important va une fois de plus être requis afin de suivre le rythme des éléments faisant partie intégrante de l’architecture de réseau. La technologie Ethernet 400G exige 50 Go dans chaque direction pour rester à jour, ce qui est supérieur au débit maximal du PCI Express Gen4. Étant donné que les bus peuvent souvent devenir le goulet d’étranglement dans une architecture x86, certaines applications avancées attendent peut-être déjà la bande passante supérieure promise par les futures générations de PCIe.

| Version | Taux de transfert | Débit/voie | Débit x 16 |

|---|---|---|---|

| PCIe 1.0 | 2,5 GT/s | 250 Mo/s | 4,0 Go/s |

| PCIe 2.0 | 5,0 GT/s | 500 Mo/s | 8,0 Go/s |

| PCIe 3.0 | 8,0 GT/s | 1,0 Go/s | 16,0 Go/s |

| PCIe 4.0 | 16,0 GT/s | 2,0 Go/s | 32,0 Go/s |

Architecture du PCIe 4.0

L’architecture du PCIe 4.0 est conçue pour fournir un débit amélioré, ainsi qu’une attribution des voies plus économique. Toute réduction de l’utilisation des broches d’E/S permise par le PCIe Gen4 équivaut à une amélioration proportionnelle en matière de consommation électrique. Par exemple, un processeur graphique utilise traditionnellement 16 voies alors qu’un pilote NVMe de PCIe 4.0 consommerait 4 voies supplémentaires. Cette différence entre PCIe x4 et x16 peut rapidement réduire les 20 à 24 voies de PCIe disponibles sur une carte mère standard.

Avec l’arrivée du PCIe Gen4, l’utilisateur a le choix entre doubler la bande passante ou diviser par deux le nombre de voies. Cette deuxième option offre plus de latitude en ce qui concerne le choix des modules d’extension en utilisant n’importe quelle combinaison de carte de dispositif PCIe x4, x8, ou x16.

L’architecture PCI Express Gen4 inclut également plusieurs fonctionnalités supplémentaires, conçues pour améliorer son efficacité et sa consommation électrique. Les marqueurs et crédits étendus pour les appareils de service constituent des fonctionnalités qui peuvent masquer la latence et optimiser la saturation de la bande passante. Des capacités supérieures en matière de fiabilité, de disponibilité et de facilité de maintenance (RAS) permettant d’augmenter les erreurs système et la virtualisation améliorée des E/S font partie des autres éléments nouveaux du PCIe 4.0. En utilisant la virtualisation des E/S, des appareils logiciels virtuels peuvent se substituer à leurs équivalents physiques, par exemple une carte réseau.

Les défis associés au PCIe 4.0

La longue liste d’améliorations architecturales intégrées au PCIe 4.0 s’accompagne de nombreux défis techniques. L’affaiblissement est plus important qu’avec les versions précédentes. Conserver l’intégrité du signal tout en s’adaptant à des exigences plus serrées en matière de marge s’est révélé un obstacle extrêmement complexe à surmonter. Du fait de la fréquence d’accompagnement plus élevée du PCIe Gen4, les longueurs de trace maximales sont passées de 16-20 pouces avec le PCIe Gen3, à 10-12 pouces.

L’augmentation de la bande passante a aussi augmenté proportionnellement les exigences en matière de performance de l’horloge de référence. Prendre les bonnes décisions en matière d’architecture d’horloge exige désormais des analyses plus approfondies pour garantir une gigue suffisamment basse et les niveaux de stabilité de fréquence, et les horloges répondant aux exigences du PCIe 3.0 ne correspondent pas nécessairement aux besoins d’un appareil PCIe 4.0.

Tests du PCIe 4.0

Les défis inhérents aux améliorations dans la conception du PCIe 4.0 se retrouvent également dans le domaine des tests. Un nouveau doublement du débit a fait apparaître des normes plus élevées en matière de capture, d’analyse, de stockage et de visualisation des données. La fréquence plus élevée et la perte de canal inhérentes au PCIe Gen4 sont autant de problèmes supplémentaires à prendre en considération pour les nouvelles applications de plateformes de test. Les tests d’horloge de référence sont devenus plus complexes, ce qui impose de tester la gigue de chacune des quatre versions et les débits de données du PCIe.

Parmi les problèmes d’équipement couramment observés lors des tests du PCIe figurent des problèmes de vitesse de liaison, de trafic et de qualité de la liaison après récupération. Un analyseur de protocole est un testeur PCI Express polyvalent qui constitue une solution efficace pour les tests et le débogage de nombreux problèmes du PCIe. Le débit amélioré du PCI Express 4.0 et la capacité à filtrer des paquets spécifiques et à enregistrer de longues séquences sont des fonctionnalités de plus en plus précieuses pour les appareils de test.

Solutions PCIe 4.0 pour l’analyse et les tests&

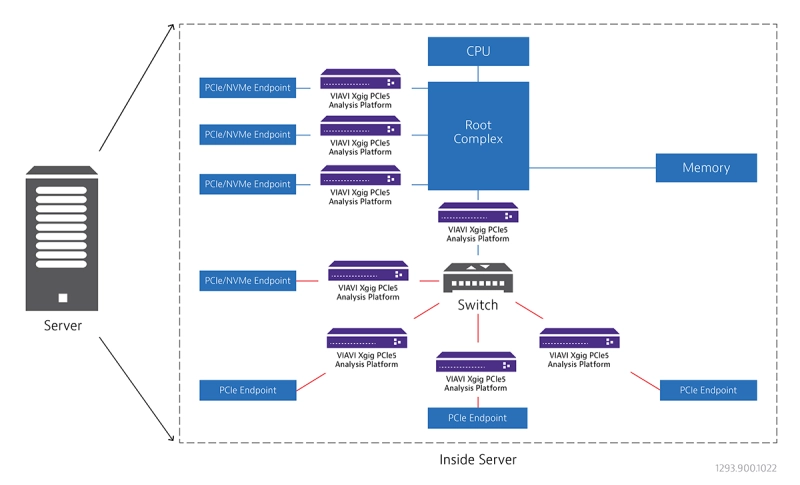

Tout au long de l’histoire de la norme PCIe, les équipements de test ont évolué et se sont adaptés pour répondre aux demandes de multiplication du débit et de complexité additionnelle au sein de l’architecture du réseau. Afin de garantir des tests précis et complets, de multiples outils et procédures doivent être utilisés.

Les analyseurs conçus spécifiquement pour le PCI Express 4.0, avec un haut niveau de visibilité au sein des flux de trafic et des capacités d’analyse de trace avancées, sont désormais devenus indispensables. Les plateformes de test telles que l’analyseur de protocoles/brouilleur Xgig 4K16 offrent également certains avantages, notamment des capacités d’injection d’erreurs et des moyens d’analyser et de brouiller simultanément sur un même châssis. La segmentation de mémoire permet quant à elle la capture de multiples traces. Les 64 Go de mémoire dans les deux directions (ascendante et descendante) fournissent également une vaste capacité de stockage pour la capture des données de trafic.

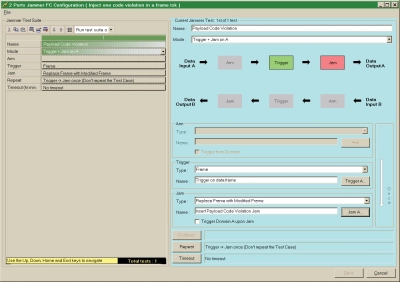

Brouilleurs

Bien que le brouillage puisse être une fonctionnalité intégrée d’un analyseur de protocoles, les produits distincts tels que le brouilleur Xgig sont capables de simuler des erreurs par manipulation du trafic en direct, vérifiant ainsi la réactivité et la robustesse du processus de récupération des erreurs. Les délais et les types d’erreurs présentés peuvent être planifiés avec précision pour que des routines de tests automatisées soient développées.

PCIe 5.0 et au-delà

Le lancement final de la spécification PCIe 5.0 a eu lieu en mai 2019. D’après PCI-SIG, le groupe responsable du lancement des différentes normes PCIe, le PCIe 5.0 a bénéficié d’un accueil enthousiaste du marché, ce qui a entraîné une accélération des cycles de développement des solutions de test et d’équipement. Les améliorations électriques propres au PCIe 5.0 ont réglé nombre des problèmes d’intégrité de signal observés avec le PCIe Gen4. Comme c’est l’usage, le PCIe Gen 5 offre également une totale rétrocompatibilité avec les versions antérieures, ainsi qu’un taux de transfert doublé par rapport au PCI Express 4.0, soit un taux phénoménal de 32,0 GT/s.

Bien que l’attente pour le PCIe 4.0 ait été inhabituellement longue, le pas de géant qu’il a représenté a justifié cette période de gestation prolongée. Avec le prochain passage aux versions PCIe 5.0, PCIe 6.0 et au-delà, la pression de la demande sur les professionnels de la conception et des tests ne devrait pas diminuer. Heureusement, une nouvelle génération d’analyseurs de protocoles et d’autres testeurs polyvalents se sont avérés en mesure de relever ce défi, ce qui est de bon augure pour l’avenir.

Découvrez le PCIe 4.0 avec VIAVI dès aujourd’hui !

Êtes-vous prêt à passer à l’étape suivante avec l’un de nos testeurs PCIe 4.0 ?

Remplissez l’un des formulaires suivants pour commencer :

Suivi à chaque étape

Nous assurons l’assistance, les services, des formations complètes ainsi que les ressources qu’il vous faut. Tout cela dans le but de maximiser la valeur de vos investissements VIAVI.

Interrogez un expert

Contactez-nous pour de plus amples informations ou pour recevoir un devis. Nos experts sont là pour répondre à toutes vos questions.