PCIe 5.0

多機能シャーシでツールの生産性を高め、TCO を削減

PCIe 5.0 は下位互換性を維持しながら、速度は PCIe 4.0 の 2 倍です。PCIe gen-5 プロトコルアナライザは、優れたメモリ、ストレージ容量、セグメントテーションで上りおよび下り回線の大量のトラフィックをキャプチャできるばかりでなく データリンク速度 32GT/秒に対応することができます。

製品

-

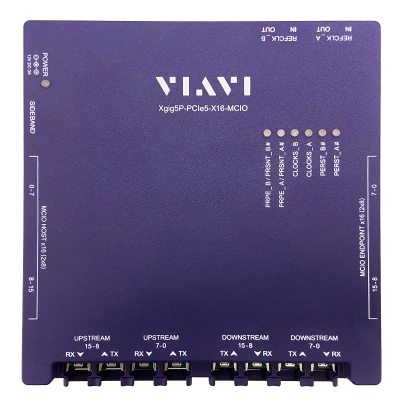

PCI Express 5.0 用 Xgig 5P16 アナライザ/エクササイザー/ジャマープラットフォーム

同じプラットフォーム上でアナライザ、エクササイズ、ジャマーの機能を組み合わせ、最新の PCIe、NVMe、CXL 仕様と同時マルチユーザーアナライザ機能をサポート

-

PCI Express 5.0 用 Xgig 5P8 アナライザ/エクササイザー/ジャマープラットフォーム

フルスピードの 32Gbps データキャプチャを提供し、PCIe プロトコルの詳細な機能とパフォーマンス分析および同時マルチユーザー機能を可能にします。

-

PCI Express® 5.0 用 Xgig エクササイザーホストテストスタンドインターポーザーモジュール

PCIe エクササイザーホストテストスタンドは、テストおよび認定のために PCIe アダプタカード端末に接続性とパワーを提供します。

-

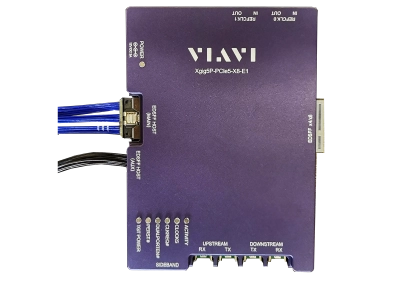

PCI Express 5.0 用の Xgig E1 EDSFF 8 レーンインターポーザ

Xgig® 5P-PCIe5-X8-E1 インターポーザは、高密度ストレージサーバーでの NVMe SSD 動作の開発、デバッグ、パフォーマンスチューニング用に最適化されています。

-

PCI Express 5.0 用の Xgig E3 EDSFF 16 レーンインターポーザ

Xgig5P-PCIe5-X16-E3 インターポーザは、高密度ストレージサーバーでの NVMe SSD 動作の開発、デバッグ、パフォーマンスチューニング用に最適化されています。

-

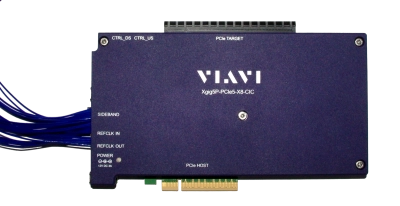

PCI Express 5.0 用の Xgig 16 レーン CEM インターポーザーモジュール

PCIe 5.0 16 レーン CEM インターポーザーは、新しい IC、新しいシステムハードウェア設計、FPGA ファームウェア、システム BIOS およびソフトウェアの検証のデバッグと検証を可能にします。

-

PCI Express 5.0 用 Xgig CEM 8 レーンインターポーザモジュール

PCIe 5.0 8 レーン CEM インターポーザは、新しい IC、新しいシステムハードウェア設計、FPGA ファームウェアのデバッグと検証、システム BIOS およびソフトウェアの検証を可能にします。

-

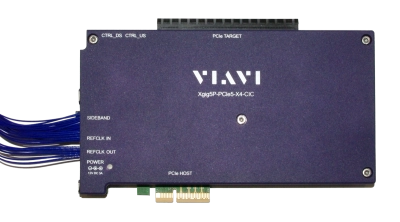

PCI Express 5.0 用 Xgig CEM 4 レーンインターポーザモジュール

PCIe 5.0 4 レーン CEM インターポーザは、新しい IC、新しいシステムハードウェア設計、FPGA ファームウェア、システム BIOS およびソフトウェアの検証のデバッグと検証を可能にします。

-

PCI Express 5.0 用の Xgig M.2 4 レーンインターポーザモジュール

PCI Express® 5.0 用の Xgig M.2、4 レーンインターポーザは、M.2 SSD 開発用に最適化設計されたアクティブインターポーザです。

-

Xgig U.2 サーバー、PCI Express 5.0 用 4 レーンインターポーザモジュール

Xgig® U.2 サーバーインターポーザは、U.2 接続を備えた高密度ストレージサーバーでの NVMe SSD 動作の開発、デバッグ、およびチューニング用に最適化されています

-

Xgig U.3 サーバー、PCI Express 5.0 用 4 レーンインターポーザ

Xgig® U.3 サーバーインターポーザは、U.3 接続を備えた高密度ストレージサーバーでの NVMe SSD 動作の開発、デバッグ、およびチューニング用に最適化されています。

-

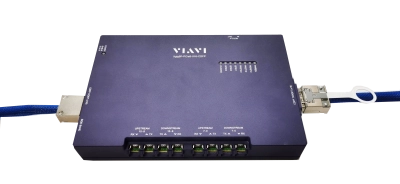

PCI Express 5.0 用の Xgig Slimline 8 レーンインターポーザモジュール

PCIe 5.0 8 レーン Slimline インターポーザは、新しい IC、新しいシステムハードウェア設計、FPGA ファームウェア、システム BIOS およびソフトウェアの検証のデバッグと検証を可能にします。

-

Xgig CDFP 16-lane Interposer for PCI Express 5.0

This PCIe 5.0 16-lane CDFP/CopprLink™ Interposer provides a tap of PCIe data signals between two externally cable-...

-

Xgig OCP3 16-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 16-lane OCP3 Interposer provides a tap of host-system PCIe signals to OCP NIC 3.0 devices for input...

-

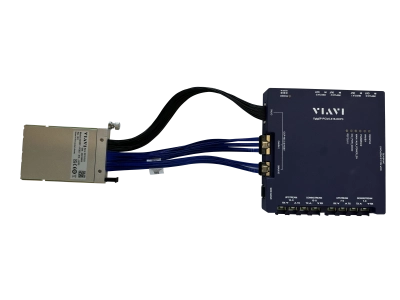

PCI Express 5.0 用の Xgig MCIO 16 レーンインターポーザモジュール

PCIe 5.0 16 レーン MCIO/CopprLink™ インターポーザにより、16 レーン MCIO/CopprLink™ ホストポートと MCIO/CopprLink™...

-

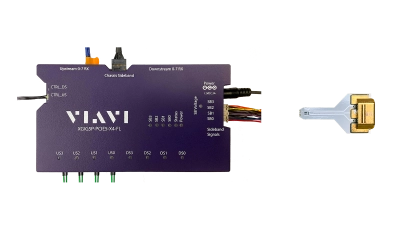

Xgig フライングリード、PCI Express 5.0 用 4 レーンプローブ

テスト対象デバイスと VIAVI プロトコルアナライザーシャーシ間のデータ信号接続を提供

-

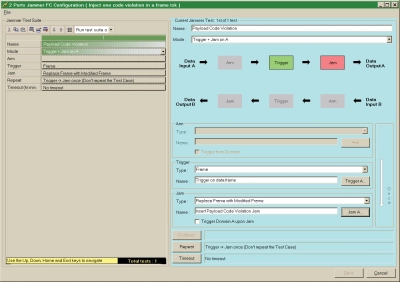

Xgig ジャマー

Xgig® ジャマーはライブネットワークトラフィックを操作することで、エラーをリアルタイムでシミュレートし、エラー回復プロセスの応答性と安定性を検証できるようにします。

-

PCI Express 5.0 用 Xgig Exerciser

PCIe Exerciser は、PCIe 5.0 プロトコルのコンプライアンステストおよび分析用の PCIe データストリームと応答を生成します。

-

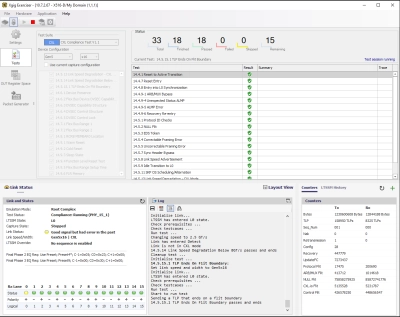

CXL v1.1/v2.0 用 Xgig エクササイザー

CXL エクササイザーは CXL ゴールドスイートのコンプライアンステスト用の承認を受けており、コンプライアンステストおよび解析用の CXL データストリームおよびレスポンスを 32GT/秒で生成します。

-

Xgig Expert

すべての Xgig アナライザには Expert ソフトウェアが標準装備されており、デバイス開発とトラブルシューティングを高速化し簡素化するように特別に設計された、デバッグおよび分析機能の独自で堅牢なセットを提供します。

-

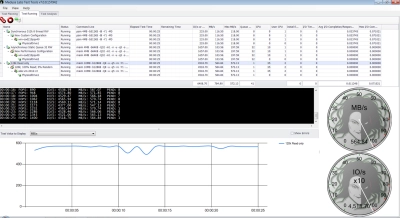

Medusa Labs テストツールスイート

Madusa Labs テストツールスイート(MLTT)は、アプリケーションベースのデータおよびシグナルインテグリティのテストツールで、開発者が製品を市場にリリースする前にストレステストを通して見つけにくいエラーを特定し、見つけ、...

データレートの大幅な高速化に伴い、新しい PCIe リリースのたびにテスト基準、テスト方法は挑戦を受けており、PCIe gen-5 も例外ではありません。例えば、EIEOS(Electrical Idle Exit Ordered Set)およびクロッキング機能に変更があると、ハードウェアレベルとシステムレベル両方のテスト方法が影響を受けてきました。

この汎用性の改善により、他のプロトコルが実績のあるPCIe物理層スタックを活用できるようになるため、代替プロトコルもテストを完全にサポートする必要があります。

- CXL(Compute Express Link)は、プロセッサ、メモリ拡張、およびアクセラレータ向けに業界が対応しているキャッシュコヒーレントな相互接続です。

- NVMe®(NVM Express®)は、ホストソフトウェアが PCIExpress®(PCIe®)、RDMA、TCP などの複数のトランスポートにまたがって不揮発性メモリと通信する方法の定義です。これは、すべてのフォームファクター(U.2、M.2、AIC、EDSFF)のソリッドステートドライブ(SSD)の業界規格です。

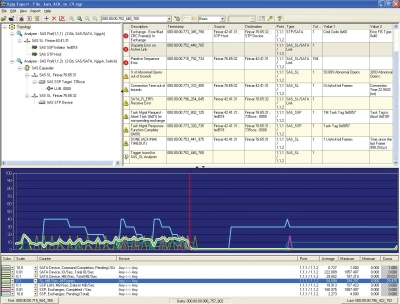

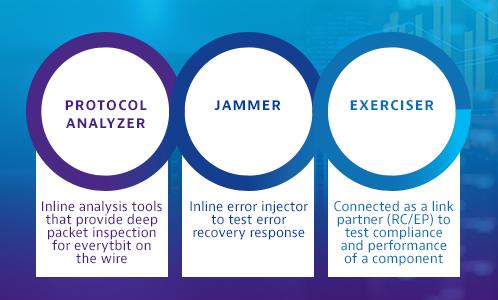

Xgig アナライザ

VIAVI Xgig アナライザなど、データリンク速度 32GT/秒に対応できる完全に下位互換のプロトコルアナライザは、 PCIe 5.0 のテストおよびデバッグを実施する上できわめて貴重です。大容量の上りおよび下りトラフィックのキャプチャのための優れたメモリとストレージ容量、およびセグメンテーションにより、特定のパケットを取り除きながら長いシーケンスを記録し、安定したプロトコル分析を実現できます。すべてのプロトコルアナライザを見る

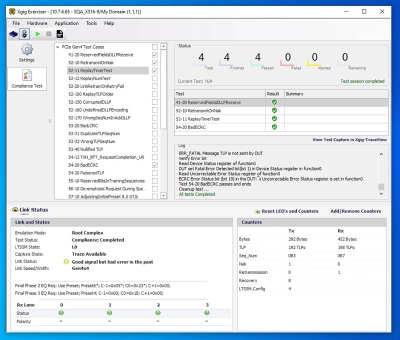

Xgig Exerciser

PCIe 5.0 用の VIAVI ソリューションズ Xgig® Exerciser は、Xgig PCIe 製品ポートフォリオにターンキーコンプライアンステスト機能を提供します。

- PCIe データトラフィックを完全にビットレベルで繰り返し制御できるため、プロトコル通信の困難な問題をデバッグするための貴重なツール

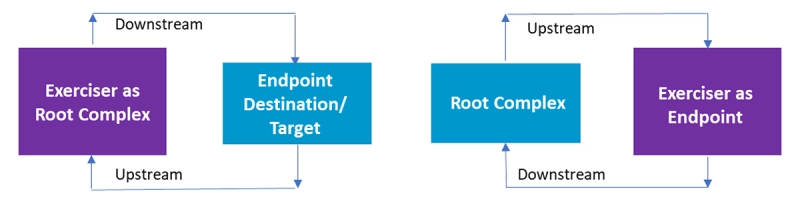

- 通信リンクパートナーを置き換え、ルートコンプレックスまたは端末テストを完全に制御(図を参照)

- コンポーネントレベルの分析とデバッグに最適

Exerciser は 2 つの動作モードがあります。ホストまたはルートコンプレックスモード(左)は、端末のテストに利用します。

端末モード(右側)は、ホストシステム、スイッチポート、および CPU のテスト利用します。

Xgig Exerciser は、PCI-SIG コンプライアンスワークショップで実施される PCI Express(PCIe)4.0 プロトコル適合認定テストで PCI-SIG (Peripheral Component Interconnect Special Interest Group)の承認を受けています。PCIe 4.0 は、PCI-SIG によって現在実施されている最高レベルの適合認定です。すべての Exerciser を見る

Xgig ジャマー

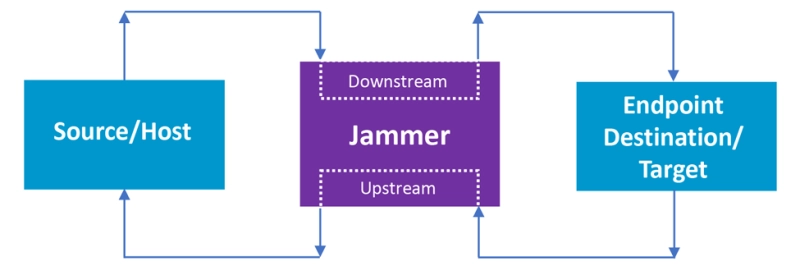

ジャマーは CPU と端末間をインラインで動作し、実際のシステムデバイス間の通信にエラーを注入します。すべてのジャマーを見る

- システムテストとエラー回復解析に最適

- リアルタイムでのネットワークトラフィックのシミュレーションにより、PCIe 5.0 ハードウェアの重要なリトマステストを作成

- デバイスが実際の環境で必要とされるとおりに動作することの確認に有用

- ミッションクリティカルな製品に不可欠

インターポーザ

インターポーザでは、ホストシステムとテスト対象デバイス(DUT)間の通信をキャプチャすることができます。VIAVI は、人気の PCIe インターポーザを幅広く揃えています。

- ホストテストスタンド

- CEM

- EDSFF、E1、E3

- U.2、U.3

- U.2 CEM

- M.2

- SFF-8674

- フライングリード

- Oculink Slimline

Xgig ツールスイート

Xgig ツールスイートは、Xgig PCIe 5.0 プラットフォームに対応しています。

- Xgig Expert™ は、迅速なデータ解釈、パフォーマンス解析、およびトラブルシューティングに役立つユーザーフレンドリーなインターフェイスです。

- Xgig Serialytics™ は Xgig Expert に基づいて、トレースで隠れた動作やイベントを明らかにします。よりコンテキストに従ったデバッグができ、シリアルプロトコルのスマートな解析が可能ないします。

- Xgig Trace Control は、事業者がシステムをテストしたいときに使用するシステム設定用のユーザーインターフェイスです。

- Medusa ラボテストツールスイート(MLTT)は、アプリケーションベースのデータおよびシグナルインテグリティテストツールであり、開発者はストレステストを通じてエラーを発見して、発生場所を特定し、解決することができます。

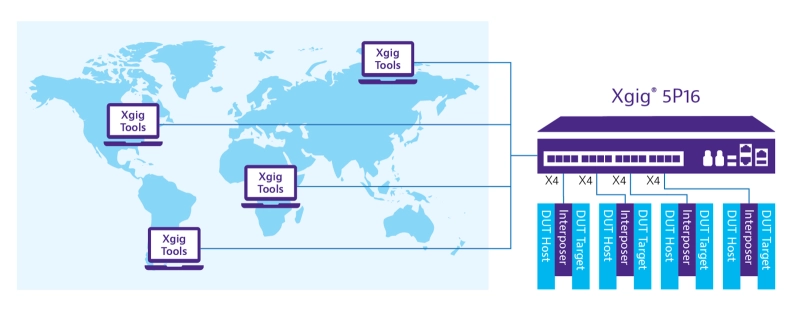

従来、PCI Express® プロトコル解析は、1 人のユーザーが専用の単一機能装置で単一のテストを実施していました。今日では、複数のユーザーが 1 つの VIAVI Xgig® 5P16 または 5P8 アナライザにログインし、同時に独立したテストを実行できるようになっています。

分岐により同時マルチユーザー(SMU)の柔軟性を実現

ユーザーは、アナライザと同じ物理的な場所にいる必要もありません。ネットワークにアクセスできる限り、世界中のどこからでもリモートログインできます。次の図は、複数のユーザーによる個別の同時テスト用に 4 つの独立したリンクに分岐した 16 レーンアナライザの例です。

分岐は、通常は 1 つのリンクであるポートを 2 つ以上のリンクに分割することで機能します。下の図に示すように、VIAVI Xgig 5P8 では、それぞれ 4 つのレーンからなる 2 つのリンクに分岐できます。また、5P16 では、それぞれ 8 つのレーンからな 2 つのリンク、またはそれぞれ 4 つのレーンからなる 4 つのリンクに分岐できます。

Xgig 5P16 シャーシ(本体)はアナライザ、Exerciser、ジャマー機能にも対応

当社の主力システムである Xgig5P16 では、同じシャーシでフル機能のアナライザ、Exerciser、およびジャマー機能に対応できます。このようなソフトウェア定義の柔軟なプラットフォームにより、機器の管理が簡素になります。ソフトウェアアップグレードは、ハードウェアモジュールよりも高速かつ経済的に提供でき、いつでも追加できるため、マネージャーはアップグレードが必要にならないかぎり資金を節約できます。

デバイスの生産性向上による市場投入時間の短縮と全体的な TCO(総所有コスト)の低下

Xgig 多機能アナライザは、単機能デバイスでは実現することが困難な運用効率を実現します。設定およびデバッグプロセスが合理化されるため、製品とコンポーネントのテストをより迅速に完了し市場に投入できるようになります。

PCI-SIG 認証テストで承認済み

Xgig Exerciser は、PCI-SIG コンプライアンスワークショップで実施される PCI Express(PCIe)4.0 プロトコル適合認定テストで PCI-SIG (Peripheral Component Interconnect Special Interest Group)の承認を受けています。PCIe 4.0 は、PCI-SIG が現在実施している適合認定の中で最高レベルの規格です。VIAVI は PCIe5 コンプライアンステストの実現において PCI-SIG と積極的に協力しています。

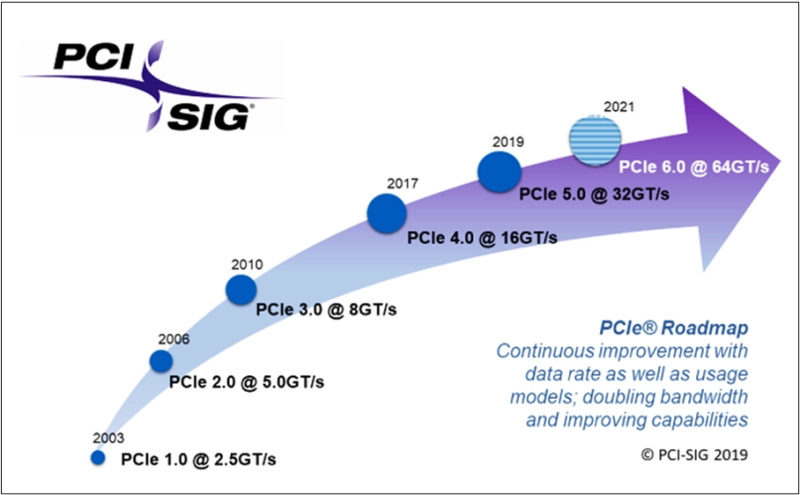

2019 年の PCI Express 5.0 規格の最終リリースは、データ集約型アプリケーションのパフォーマンス要求の増大への対処に必要とされると見なされていた 18 か月の高速開発サイクルの到達点です。

PCIe スロットと接続カードの間の最小バージョン(速度)はゲーティングファクタのままですが、前世代と同様に、PCIe 5.0 は過去のイテレーションとの下位互換性を維持しています。帯域幅の増加に加えて、PCIe 5.0 仕様には、信号のインテグリティを向上させるための電気的な拡張機能や、コネクタの性能を向上させるための機械的な更新機能も含まれています。

連続する各 PCIe リリースと同様に、PCIe インターフェイスの固有の下位互換性により、PCIe Express 5.0 と以前の PCIe バージョンの共存が可能になり、クラウドコンピューティングや人工知能(AI)などの最も要求の厳しい高性能アプリケーションは最高の転送速度を活用でき、同時に前世代のテクノロジーも要求の厳しくないアプリケーション向けに引き続き使用できます。

2019 年の PCIe 5.0 のリリース日は、実装までの道のりの数多くある段階の第一段階です。また、事前のコンプライアンスと相互運用性テストも成功裏に完了する必要があります。こうした追加のマイルストーンにより、最初の認証済みの PCIe 5.0 商用製品の販売開始は、さらに先に伸びる可能性があります。

PCIe は、現在使用されているほぼすべてのタイプのコンピューティングシステムに組み込まれており、PCI Express 5.0 の代表的な顧客およびサプライチェーンインフラには、エレクトロニクス、コンピューティング、データストレージ、E コマース業界の世界最大の企業が多数含まれています。これには、PCIe Gen 5 機能を実現する知的財産(IP)サプライヤ、スイッチおよびリタイマーのメーカー、PCIe 5.0 マザーボード、ストレージデバイス、およびグラフィックスコントローラサプライヤが含まれます。これらの基本的な構成要素は、データセンターやその他の基本的なネットワーク展開のために、高度なコンピュータシステムやハードウェアに組み込まれます。

PCIe 5.0 早期採用の市場セグメント

必ずしもすべての企業および市場セグメントが PCI Express Gen 5 テクノロジーを同時に採用するとは考えられていません。IP 市場では、FPGA またはシリコン形式での機能保証に、早期検証機能が必要になります。CPU、イーサネット、および一部のアクセラレータセグメントも、PCIe 5.0 の早期採用に深く関わることになります。データセンターサーバーとハイパフォーマンスコンピューティング(HPC)インフラは、拡大し続ける帯域幅とレイテンシの要求に対応するのにすでに悪戦苦闘しており、PCIe Gen 5 テクノロジーが利用可能になった時点で、その生来の利点をすぐに吸収すると考えられます。

PCIe 5.0 プロトコル解析ユーザー

検証およびデバッグサイクルの迅速化は、市場投入までの時間の短縮に不可欠です。これにより、検証と妥当性確認を行うシステム統合チームおよびコンポーネントの適格性確認と相互運用性の問題解決に取り組むデバッグチーム向けの高度な PCIe Gen 5 プロトコル分析ツールへの需要が高まります。デバイス、ドライバー、およびアプリケーションソフトウェアのパフォーマンス調整チームは、高度な PCIe 5.0 プロトコル分析機能から高い投資収益率を得られます。

PCIe の倍速化の取り決めは、PCIe 5.0 のリリースでも有効です。PCIe 5.0 は、PCIe バージョン 3.0 以降標準となっている 128b/130b エンコーディング方式を使用して、各方向で 64 GB/秒のスループットを提供します。PCIe テクノロジーにより、データは双方向で全二重に流れることができるため、両方向の総スループットは合計で 128GB/秒になります。

PCIe 3.0 より前のエンコード規格は 8b/10b で、8 ビットのデータがエンコードされ、10 ビットの数値として送信されました。これにより、未加工ビット転送レート 2.5 GT/s をわずか 2.0 Gbit/秒の正味帯域幅に削減する 20% のパフォーマンスオーバーヘッド要因が発生しました。この効率的な 1.5% のオーバーヘッドファクターは、PCIe 5.0 エンコーディングの規約でも有効です。

PCIe のバージョン |

リリース 年 |

転送レート |

スループット/レーン |

x16 スループット |

1.0 |

2003 年 |

2.5 GT/秒 |

250 MB/秒 |

4.0 GB/秒 |

2.0 |

2007 年 |

5.0 GT/秒 |

500 MB/秒 |

8.0 GB/秒 |

3.0 |

2010 年 |

8.0 GT/秒 |

1.0 GB/秒 |

16.0 GB/秒 |

4.0 |

2017 年 |

16.0 GT/秒 |

2.0 GB/秒 |

32.0 GB/秒 |

5.0 |

2019 年 |

32.0 GT/秒 |

4.0 GB/秒 |

64.0 GB/秒 |

PCIe 5.0 の驚異的な速度では、PCI 5.0 マザーボード上の一般的なブルーレイディスクの内容を 1 秒以内に不揮発性メモリ(NVM)に転送できます。このような卓越した速度は贅沢なように見えるかもしれませんが、他の分野のネットワークアーキテクチャの機能追加によって必要になってきました。例えば、400G イーサネットでは、最大容量の CPU とインターフェイスをとるために、各方向に 50GB/秒の帯域幅が必要です。

PCIe 4.0 でフルサイズの x16 スロットで利用できる 32 GB/秒では不十分であることが判明しています。PCIe 5.0 テクノロジーを使用すると、使用可能な帯域幅は、このインターフェイスの要件を超え、まだ余裕があります。

イーサネットに加えて、この継続的な改善サイクルは、自動運転、瞬時の応答を必要とする防御アプリケーション、ハッキングを即座に阻止する必要がある重要な財務セキュリティアプリケーションなど、レイテンシがクリティカルなパフォーマンス要件を持つリアルタイムシステムの出現によって促進されています。マルチ GPU システムとプレミアムグラフィックスカードの個々のユーザーは、PCIe 5.0 の速度と帯域幅の拡張によって、目に見えるメリットも得られます。

PCIe 5.0 の仕様は、このイテレーションに固有のリンクやトランザクションレイヤーの変更が含まれない、下位互換性のある PCIe 規格の自然な進化と分類される場合があります。PCIe 5.0 の仕様は、PCIe 4.0 で確立された拡張フロー制御と拡張タグおよびクレジットの利点を継承しています。

アドインカード用に指定された新しい CEM コネクタが追加されました。シグナルインテグリティおよびコネクタ設計機能の改善により、全体的な性能と信頼性が向上しています。物理レイヤーの機能追加には、EIEOS、SKP オーダーセット、およびイコライゼーションシーケンスの更新も含まれます。

PCI Express 5.0 の仕様は、一般にハードウェアメーカーや業界関係者から高く評価されています。特に、テスト容易性の向上、リンクトレーニングの高速化、代替プロトコルサポートの提供を実現するための機能追加は、PCIe 5.0 の非常に優れた特性として認識されています。この業界コンセンサスと、PCIe 4.0 から PCIe 5.0 への移行に必要な比較的穏やかな一群の実装条件により、積極的なハードウェア開発と商用化目標が先導されてきました。

PCIe 5.0 のリリースに伴う進歩と仕様の変更により、テストおよび開発作業を複雑にする PCIe のアーキテクチャ上の課題の多くがさらに増しています。これには、トランスミッタ(Tx)ジッターの 2 倍の低減要件と、リファレンスクロックジッターの 3 倍の削減などがあります。

信号損失は、PCIe 5.0 でも継続的なアーキテクチャ上の課題となっています。リタイマー、リドライバー、および代替プリント基板(PCB)のベースマテリアルは、これらの問題を軽減するためにハードウェア設計者が利用できるいくつかの費用対効果オプションです。リタイマーを使用して信号を再送信したり、リドライバーを使用して信号を増幅したりできます。どちらの方法でも、リンクの物理的な到達範囲を改善できます。

PCI Express 5.0 の仕様では、チャネル損失バジェットは 36dB と定義されていますが、これは、PCIe 4.0 しきい値よりも最大わずか 28% 大きいだけです。PCIe テクノロジー固有の挿入損失は PCIe 5.0 リリースでも継続されるため、FR4 PCB 構造で発生する損失レベルはもはや維持できず、また、最大で FR4 の 2.5 倍のコストがかかるメガトロンなどの代替材料が必須となりました。また、PCI Express 5.0 のチャネル要件により、トランスミッター(TX)およびレシーバー(RX)の新しいイコライゼーション回路デザインも必要となり、電圧とタイミングの両方で Rx でのレーンマージニングが必須となりました。

PCIe 4.0 から PCI Express 5.0 への移行にあたっては、2 倍の高速化、下位互換性、およびリリースサイクルの高速化が、実行戦略を構築する 3 つの基本となる柱でした。

速度の向上を有効またはサポートする新機能は、他の推奨または要求された変更よりも優先されました。例えば、速度の向上を有効にするには EIEOS とデータビットレート定義の変更が必要でしたが、エンコーディング方式やターゲットビットエラーレート(BER)などの基本的な PCIe エレメントは一定のままでした。また、信号方式とスクランブル方式も PCIe Gen 4 と一貫性を保ち、実装への影響を最小限に抑えるために、可能な限り既存のトランスミッタ(Tx)およびレシーバ(Rx)テスト方式が活用されました。

市場投入までの時間と互換性を重視したにもかかわらず、PCIe 4.0 と PCIe 5.0 の間の他の重要な設計変更は、当然のことながら、接続するハードウェアとテスト慣行に影響を及ぼしました。アドインカードインターフェイスでは下位互換性が維持されていますが、セカンドオーダー応答を備えたクロックデータリカバリ(CDR)と、表面実装型 PCBA フットプリントとのみ互換性のある CEM コネクタなどは影響を受けました。PCI Express 5.0 は、TS1/TS2 シーケンスを変更することで代替プロトコルにも対応しています。

ネットワークの状況と帯域幅の需要がバックグラウンドで拡大し続け、4.0 規格のリリース時間が非常に長くなったため、PCIe 4.0 規格と PCIe 5.0 規格の一貫性がさらに必要となりました。これにより、2 つの規格間のオーバーラップ期間が事実上保証され、設計とテストの手法の共通性がスムーズな移行に不可欠なものになりました。

PCIe 5.0 物理レイヤーの更新

PCI Express Gen 5 のリリースに伴う、より厳格なジッター要件、チャネル損失バジェットの制約、および電圧と時間に関するレーンマージン要件に加え、物理レイヤーの追加的な変更が高速化によって必要になった一方、以前の PCIe バージョンとの下位互換性を維持するために必要な他の進歩もありました。

オーダーセットの変更は、PCI Express 5.0 仕様のリリースに伴う重要な変更でした。EIEOS オーダーセットは、電気的アイドル状態からの退出を容易にするために使用されます。PCIe 4.0 の各オーダーペアに使用される 16 個の 0 と 1 の使い慣れたパターンが、PCIe Gen 5 規則では、32 個の 0 と 1 が各レーンで繰り返されることになりました。バックツーバック(繰り返し)EIEOS 信号は、PCIe 5.0 プロトコルの追加変更です。また、PCI Express Gen 5 データストリームの起点をレシーバーで明確に識別できるように、データストリームオーダーセットスタート(SDS)も更新されました。

トレーニングシーケンス(TS1/TS2)は、PCIe Gen 5 の速度倍増を容易にすることを目的とした革新的な新しいオプションの恩恵を受けています。トレーニングシーケンスは、リンクの立ち上げとイコライゼーション(EQ)に必要な先行作業ですが、2.5GT/秒から段階的に移行して 32.0GT/秒 PCIe Gen 5 の速度にするまで、オーダーされたセットでスピードへのインクリメント対応を進めるたびに遅れが発生する可能性もあります。このジレンマを解決するために、EQ バイパスオプションが用意されており、基本的に中間速度のイコライゼーションレベルを「スキップ」したり、L0 アクティブデータ転送状態への即時移行のために「No EQ」オプションを使用してイコライゼーションを完全に省略したりすることができます。

また、PCIe 5.0 の変更された TS1 および TS2 に、代替プロトコル ID および拡張プレコーディングサポートのための新しいフィールドも追加されました。システムとデバイス間のネゴシエーションが成功すると、リンクはただちにサポートされている最高速度で L0 状態に移行し、ネゴシエートされた代替プロトコルを使用してデータの転送を開始できます。代替プロトコルのネゴシエーションが失敗した場合、システムはバックボーンの PCI Express 5 プロトコルに素早く復帰できます。

ほぼ無制限のリンク条件とシナリオにより、PCIe 5.0 リンクアクティビティの起動(L0 より前)フェーズと完全起動(L0)フェーズの両方でトラブルシューティングの課題が発生します。最高の PCIe Gen 5 テストソリューションにより、階層化された体系的なアプローチが可能になり、継続的にシステムパフォーマンスメトリックスを改善しつつ、トラブルシューティングの時間と労力を大幅に削減できます。

リンクトレーニングとステータス状態マシン(LTSSM)の状態中に確認されるリンク起動の問題には、シグナルの完全性と検出の問題、正しくないリンク速度、およびプロトコルアナライザを使用して効果的に診断できるその他の潜在的な状態などがあります。L0 状態になった後は、高度な PCIe プロトコルアナライザを使用して、プロトコルスタックのさまざまなレイヤーでの過剰なリプレイ、復元の問題、遅延などのパフォーマンス上の非効率性を効率的に検出し、緩和することもできます。

正確な診断機能を必要とする 1 つの一般的な PHY レイヤーの状態は、電気的アイドル(EI)から脱出中に発生します。この状態では、Tx ロジックと Rx ロジックの不一致によってレイテンシが発生する可能性があります。VIAVI Xgig アナライザは、短いロック時間と高度な後処理機能を採用することで、これらの条件を確実に特定し、低パワー状態の遷移中にキャプチャされるデータの損失を最小限に抑えます。

物理レイヤーのリアルタイムメトリックスは、リンクの全体的な信号の健全性と復元データを監視するために極めて重要です。例えば、リンクが L0 状態で動作している場合、リプレと復元が繰り返され、システムパフォーマンスが大幅に低下する可能性がありますが、多くの場合、検出されません。レーンごとの解像度を備えた Xgig リアルタイム監視、メトリックス、およびポストキャプチャ分析機能により、非確認応答(NAK)、リプレイ、リンクエラー、およびレシーババッファオーバーフローや過剰なトランザクションキュー深度などのフロー制御(FC)統計を効果的に監視および診断できます。

PCIe リリース日の非常に速い周期は、今後も続くと思われ、PCIe 6.0 の最終仕様のリリースは、2021 年に予定されています。この新しいイテレーションでは、 PCIe の標準となっている従来の帯域幅の倍増と下位互換性が継続され、今回は双方向帯域幅が驚異的な 256 GB/秒に達します。これにより、PCIe は実質的にローエンド GPU の VRAM 帯域幅と同等となります。

さらに 2 倍の速度向上を実現し、高い信頼性基準を維持するために、パルス振幅変調(PAM4)と前方誤り訂正(FEC)技術が採用されます。人工知能とマシンラーニングは、そのパフォーマンスが並外れた速度、低レイテンシ、複数の周辺機器への同時高速アクセスの組合せに依存しているため、この機能拡張の恩恵を受けると考えられます。

PCIe Gen 5 は、I/O バステクノロジーの新たな飛躍的な進歩です。PCIe 5.0 の仕様は、近い将来にわたって、ネットワークアーキテクチャのボトルネックを解消しながら、ムーアの法則に遅れをとらずに進んでいくでしょう。改善された新しい PCIe 5.0 テストツールが毎日登場しているため、この進歩は PCIe 6.0 のリリースと今後の多くの世代を通じて継続していくものと考えられます。

あらゆるステップでのサポート

VIAVIは、サポート、サービス、総合的なトレーニング、お客様が必要とするリソースを提供しています。これはすべて、お客様のVIAVIへの投資価値を最大化するために当社が日頃より行っていることです。

エキスパートに尋ねる

詳細、価格のお見積りについてお問い合わせください。Viaviのエキスパートがお客様のあらゆる質問にお答えします。