Compute Express Link (CXL)

Compute Express Link Guide and Resources

Compute Express Link technology is rapidly evolving to address memory allocation and data storage challenges brought on by artificial intelligence and machine learning applications. Advanced analysis solutions from VIAVI help operators to support the unique test and validation requirements of the CXL standard.

Продукты

-

Xgig 6P16 Analyzer / Exerciser for PCI Express 6.0

Fully integrated, 16-lane PCIe6 Analyzer/Exerciser solution with support for CXL and NVMe

-

Xgig 5P16 Analyzer / Exerciser / Jammer Platform for PCI Express 5.0

Combines A/E/J functionality on the same platform with support for the latest PCIe, NVMe and CXL specifications, and...

-

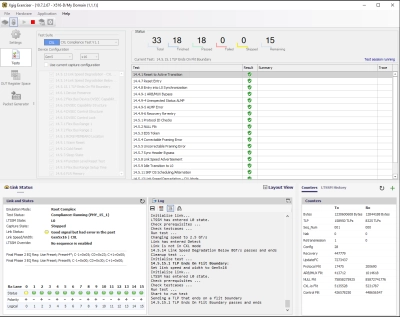

Xgig Exerciser for CXL v1.1/v2.0

Approved for CXL Gold Suite compliance testing, the CXL Exerciser generates CXL data streams and responses for...

As a participating member of the CXL Consortium, VIAVI has recognized the growing industry consensus surrounding Compute Express Link topology. Decades of high-speed interconnect testing experience have uniquely qualified VIAVI to lead vital CXL decode validation efforts and participate in ongoing specification development with a customer-centric perspective.

An industry-leading portfolio of PCIe® protocol analyzers, jammers, exercisers, and test software spanning multiple generations of the standard has allowed VIAVI to pivot naturally to CXL test processes over the same physical interface. Real time metrics, transaction analytics, and detailed capture and analysis of CXL bring-ups are now available in versatile and intuitive test platforms.

Поддержка на каждом этапе работы

Мы оказываем техническую поддержку, предоставляем услуги, программы обучения и все необходимые материалы. Наша деятельность направлена на максимальное повышение отдачи от ваших капиталовложений в систему VIAVI.

Спросите у специалиста

Обращайтесь к нам для получения дополнительной информации и ценовых предложений. У нас есть специалисты, готовые дать правильный ответ на любой ваш вопрос.