Compute Express Link(CXL)

Compute Express Link のガイドとリソース

Compute Express Link テクノロジーは、人工知能と機械学習アプリケーションによってもたらされるメモリ割り当てとデータストレージの課題に対処するために急速に進化しています。VIAVI の高度な分析ソリューションは、通信事業者が CXL 規格の独自のテストおよび検証要件をサポートするのに役立ちます。

CXL コンソーシアムの参加メンバーとして、VIAVI は、Compute Express Link トポロジーに関する業界のコンセンサスが高まっていることを認識しています。何十年にもわたる高速相互接続テストの経験から、VIAVI には、重要な CXL デコード検証の取り組みを主導し、顧客中心の視点で進行中の仕様開発に参加する独自の資格があります。

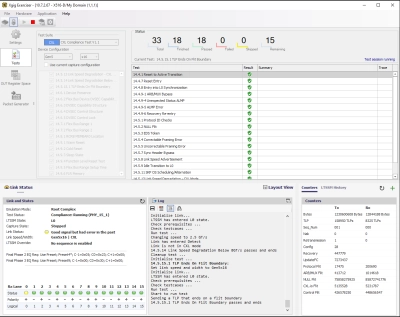

PCIe® プロトコルアナライザ、ジャマー、エクササイザー、および複数世代の規格に対応するテストソフトウェアの業界トップのポートフォリオにより、VIAVI は同じ物理インターフェイスを介して CXL テストプロセスに自然に移行することができました。リアルタイムのメトリクス、トランザクション分析、および CXL ブリングアップの詳細なキャプチャと分析が、多目的で直感的なテスト プラットフォームで利用できるようになりました。

Compute Express Link とは

CXLは、メモリやその他のデバイスへの高速 CPU 接続のためのキャッシュコヒーレントなオープンインターコネクト規格です。Compute Express Link は、標準の PCIe 5.0 物理レイヤーを活用し、サポートされている代替プロトコルとして実行されます。接続されたデバイスに共通のメモリ空間を作成することにより、CXL 規格は、ハイパースケーラーおよびその他の高度なアプリケーションにパフォーマンス上の利点をもたらします。

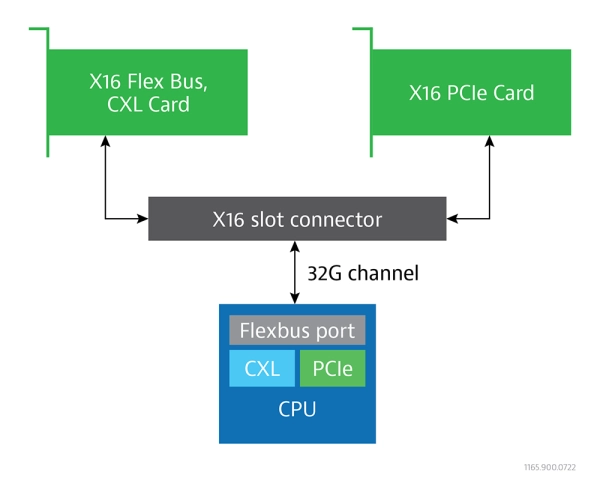

- Compute Express Linkは、PCIe 5.0または CXL モードどちらでも動作可能な柔軟なプロセッサポートを利用しています。どちらのデバイスクラスも、16 レーンの各方向で 32GT/秒または最大 64GB/秒のデータ転送速度を達成できます。

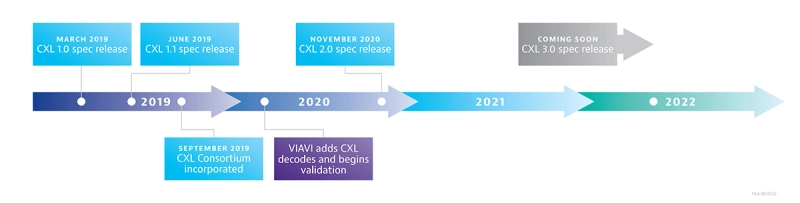

- CXL コンソーシアムは、技術仕様の開発、新しいユースケースモデルのサポート、CXL テクノロジーの開発と採用の促進を目的として、2019 年に業界をリードする 9 つの組織によって設立されました。

- 人工知能(AI)、機械学習、およびクラウドインフラは、CXL インターフェイスによって提供される非常に低いレイテンシとコヒーレントなメモリーアクセスから最も恩恵を受けるアプリケーションの 1 つです。

CXL はどのように機能しますか?

要約すると、Compute Express Link フレームワークは、CPU のメモリーと接続された各デバイスとの間のコヒーレンシーを確立します。これにより、ソフトウェアスタックの複雑さが軽減されても、ストレージリソースを効率的にプールして共有できます。メモリープールを有効にするには、ホストデバイスと周辺デバイスの両方が CXL 対応である必要があります。データ転送は、528 ビットのフロー制御単位「フリット」を使用して行われます。

- シングルレベルスイッチングを使うと、ホストは、各方向で高いスループットを維持しながら、複数のデバイスにファンアウトできます。アクセラレーターや使用可能な CXL ストレージなどのリソースは、サーバーのワークロードの変化に応じて動的に再割り当てできます。

- CXL 2.0仕様には、標準化されたファブリックマネージャーも含まれます。これにより、プーリングの種類、ホスト、または使用モデルに関係なく、一貫した構成とエラーレポートでシームレスなユーザーエクスペリエンスが保証されます。

一般的な Compute Express Link のユースケース

インターフェイスが進化するにつれて、独自のユースケースとアプリケーションにより、CXL コンソーシアムは、3 つの個別のデバイスタイプを定義するようになりました。

- タイプ 1 デバイス:ローカルメモリーがないために CPU に依存する必要があるアクセラレータやその他のデバイスは、タイプ 1 に分類されます。CXL.io および CXL.cash プロトコルにより、これらのデバイスはより効率的に通信して、ホストプロセッサからメモリー容量を移動できます。

- タイプ 2 デバイス:独自のデータストレージ機能を備えているだけでなく、CPU メモリーも活用する製品は、タイプ 2 として知られています。3 つの CXL プロトコルをすべて組み合わせることにより、これらのデバイスと CPU の間でコヒーレントメモリー共有が促進されます。

- タイプ 3 デバイス:既存の CPU メモリを増強するように設計されたメモリエクスパンダーまたはデバイスは、タイプ 3 に分類されます。CXL.io および CXL.memory プロトコルにより、CPU はこれらの外部ソースにアクセスできるようになり、帯域幅とレイテンシのパフォーマンスが向上します。

Compute Express Link の利点

接続性とリソース共有を合理化することにより、CXL テクノロジーは、システムの複雑さとコストを削減しながら、大容量ワークロードのパフォーマンスを向上させる多数の拡張機能を提供します。これらの属性は、次世代のデータセンターと新技術によって、データ処理の高速化と総所有コスト(TOC)の削減に対する需要が高まるにつれて、ますます価値が高まっています。

- コヒーレンシーにより、CXL メモリープールはデータの有効性に関して一貫性を維持できます。これにより、デバイスとプロセッサー間でより高速かつ効率的にリソースを共有できるようになります。

- CXL 規格は、さまざまなタイプと世代のプロセッサを組み合わせた異種アーキテクチャに完全に対応しています。これは、インフラの要素が進化するにつれ、複雑な AI ニューラルネットワークや機械学習システムに特に役立ちます。

- 低レイテンシは、戦略的にプールされた永続メモリー、改善された CXL スイッチング効率、および標準化されたメモリー管理の結果です。レイテンシの短縮は、次世代のユースケースと将来のPCIe6.0の採用の重要なイネーブラーと考えられています。

CXL プロトコルと規格

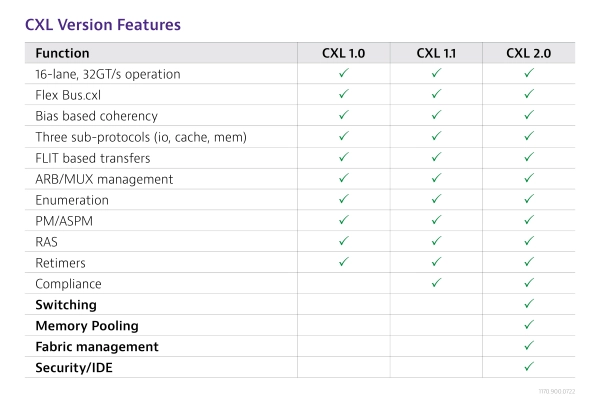

2019 年の CXL 1.0規格のリリースは、共有アクセラレータデバイスメモリーへの CPU アクセスを特徴とする重要なマイルストーンでした。Compute Express Link プロトコルと規格は、この成功したデビュー以来、改善と拡大を続けています。

- CXL 1.1は、リリース 1.0 との下位互換性を維持しながら、元の規格のコンプライアンスと相互運用性の側面を改善しました。

- CXL2.0 は、リソースのオーバープロビジョニングの必要性を最小限に抑えながら、ファンアウト構成、リソースプーリング、および永続メモリーサポート用のスイッチング機能を追加しました。リンクレベルの完全性とデータ暗号化(CXL IDE)もセキュリティ向上のために導入されました。

- CXL 仕様 1.0 用に開発されたサブプロトコルは、Compute Express Link のライフサイクル全体で一貫性を保っています。

- CXL.io は、PCIe 5.0 プロトコルに基づいており、検出、構成、および登録アクセス機能に使用されます。CXL.io が機能するには、すべての Compute Express Link デバイスでサポートされている必要があります。

- CXL.cacheは、CPU(ホストデバイス)とその他の Compute Express Link 対応デバイスとの間の相互作用を管理します。このサブプロトコルは、ホストメモリーの効率的で低レイテンシのキャッシュと、リクエストとレスポンスのプロセスを使用した CPU メモリーへのデバイスの直接アクセスをサポートします。

- CXL.memoryは、load コマンドと store コマンドを使用して、ホストが接続されたデバイスメモリーをプロビジョニングするためのアクセスモードを提供します。この構成では、CPU がマスターとして機能し、Compute Express Link デバイスが従属として機能します。

ストレージに対する CXL の影響

CXL プロトコル仕様によって定義された異種のオープンコンピューティングモデルは、より柔軟なストレージ状況を生み出し、効率的なデータ移動により、レイテンシの短縮とコストの削減に貢献します。プールされたコヒーレントメモリーの潜在的な価値を超えて、独自のメモリー相互接続の削減は、新しいテクノロジーデバイスの多様性を補完することになります。

このストレージダイナミクスの変化により、キャッシュされたメモリープールのサイズも増加し、ハイパースケールデータセンターやその他の大規模なコンピューティングエンタープライズの一時ストレージのニーズを満たすのに役立ちます。CXL メモリープーリングによって生み出される追加の容量は、大量のワークロードの必要に応じて呼び出すことができます。このストレージパラダイムの変化は、データセンターの細分化とオープンアーキテクチャへの全体的な傾向と一致しています。

CXL および PCIe

PCI Express(PCIe)は、過去 20 年間で、接続されたデバイスへの高速リンクを提供するポイントツーポイントトポロジーを備えた、事実上の高速シリアルバスアーキテクチャになっています。バルクデータ転送に対する PCIe の能力にもかかわらず、大規模なデータセンターアプリケーションでは欠点が明らかになります。メモリープールは互いに分離されたままであるため、大量のリソースを共有することはほとんど不可能であり、新しく接続されたデバイスのためにレイテンシ欠陥が増加します。

- PCIe 5.0は、下位互換性のある最新世代の周辺コンポーネント相互接続エクスプレス(Peripheral Component Interconnect Express)規格です。2019 年にリリースされた第 5 世代には、CXL インターフェイスで現在利用されている代替プロトコル展開のサポートとともに、必要なスループットの倍増が含まれています。

- CXL プロトコルは、PCIe 5.0 物理レイヤー上で動作し、トランザクションレイヤー内に新しいメモリー共有機能を統合することにより、標準の PCIe アーキテクチャの多様性を踏まえています。

- 標準の PCIe デバイスおよび CXL ソフトウェアは、同じリンク上でサポートできます。柔軟なプロセッサーポートは、標準 PCIe または代替プロトコル CXL 相互接続トランザクションのいずれかをすばやくネゴシエートできます。

- PCIe 6.0 の速度は、以前の世代の倍増規則を継続します。これにより、デバイスとシステムメモリーの融合は、レイテンシの削減とアクセラレータのパフォーマンスにとって不可欠な考慮事項になります。

CXL 対 CCIX

CXL の直接のライバル技術として機能するのではなく、アクセラレータ用キャッシュコヒーレントインターコネクト(CCIX®)は、メモリープーリングに別のアプローチを採用しています。

- CCIX コンソーシアム:CCIX コンソーシアムが表明した使命は、効率的な異種コンピューティングのために、汎用プロセッサとアクセラレーションデバイス間のコヒーレントインターコネクトテクノロジーを実現する業界標準仕様の開発と採用の促進です。

- CCIX の仕様:オープンソース仕様は、メモリーコヒーレンスのピアツーピア対称モードを定義し、CXL 仕様と並行して(年代順に)開発されてきました。複数のデバイスからのストレージ容量は、不均一なメモリーアクセスアーキテクチャ(NUMA)を使用して一緒にプールされます。ホストデバイスとアクセラレータの両方が CCIX 動作をサポートしている必要があります。

- 代替プロトコル:CCIX と Compute Express Link はそれぞれ、PCIe 5.0 物理レイヤーと代替プロトコルのサポートを活用します。FlexBus 接続を使用すると、CXL テクノロジーはデフォルトでキャッシュの一貫性のために CPU を使用しますが、CCIX はデバイス階層を確立しません。この違いにより、Compute Express Link アーキテクチャの速度とレイテンシにおおきな利点がもたらされました。

VIAVI CXL 製品

PCIe 5.0 用の VIAVI Xgig アナライザソリューションは、CXL.cache/memory トランザクションとトリガーをサポートします。Xgig は貴重なリアルタイムメトリックスをキャプチャし、複数のトレースに対して同時に詳細な分析を実行します。

Xgig PCIe 5.0 16 レーン CEM インターポーザのような VIAVI PCIe 5.0 インターポーザは、PCIe 物理レイヤーで実行されている CXL トラフィックをキャプチャするために使用できます。インターポーザは、プロトコルアナライザとテスト対象システム間の双方向インターフェイスを形成します。

VIAVI と CXL コンソーシアム

CXL コンソーシアムは、データセンターアクセラレータやその他の高速機能強化のためのオープンエコシステムをサポートしながら、新しい使用モデルの画期的なパフォーマンスを促進する技術仕様を開発するために結成されたオープン業界標準グループです。

コンソーシアムは、2019 年に 9 つの創設組織によって正式に法人化され、現在、約 170 のメンバー企業が参加しています。これには、理事会を構成する 15 の大手コンピュータ業界組織が含まれます。

VIAVI は、CXL コンソーシアムの誇り高いメンバーであり、数十年にわたる高速シリアルバスのテストおよび検証の専門知識を、独自のテスト要件の進化に合わせて、新しいワーキンググループおよび仕様開発に貢献しています。VIAVI は、2020 年初頭に Compute Express Link 用の基本検証ワークフローを開始しました。

Compute Express Link の歴史

CXL は、CXL 1.0 仕様のリリースにより、2019 年 3 月に初めて世界に紹介されました。マイナーアップデートのみを含む CXL 1.1 は、わずか 3 か月後にリリースされました。2020 年 11 月のバージョン 2.0 に代表される大幅なアップグレードには、リンクスイッチング、リンクセキュリティ、およびシステムパフォーマンスと迅速な採用に直接関係するその他の重要な機能が含まれました。CXL over Ethernet などのアプリケーションのリソースを確実に追加または削除するために、ホットプラグフローも定義されました。

- 市販された最初の Compute Express Link 対応製品は、2019 年 4 月に発売された Agilex™FPGA の Intel® ファミリーのものでした。

- その他の CXL 製品の紹介には、Samsung によるメモリー拡張モジュールと、多くの主要メーカーのプロセッサが含まれています。

- 複数の Compute Express Link デバイスが現在開発中であり、信頼性の高い CXL プロトコル分析および検証ソリューションの必要性を浮き彫りにしています。

- CXL 2.0 は現在利用可能です。PCIe 6.0 物理レイヤーに適応する CXL 3.0 は、2022 年にリリースされる予定です。

あらゆるステップでのサポート

VIAVIは、サポート、サービス、総合的なトレーニング、お客様が必要とするリソースを提供しています。これはすべて、お客様のVIAVIへの投資価値を最大化するために当社が日頃より行っていることです。

エキスパートに尋ねる

詳細、価格のお見積りについてお問い合わせください。Viaviのエキスパートがお客様のあらゆる質問にお答えします。