PCIe 5.0

Die schnellste und robusteste PCI-Express-Leistung

Produkte

-

Xgig 5P16 Analyzer/Exerciser/Jammer Platform for PCI Express 5.0

Combines A/E/J functionality on the same platform with support for the latest PCIe, NVMe and CXL specifications, and…

-

Xgig 5P8 Analyzer/Exerciser/Jammer Platform for PCI Express 5.0

Provides full-speed 32Gbps data capture, enabling detailed functional and performance analysis of PCIe protocol…

-

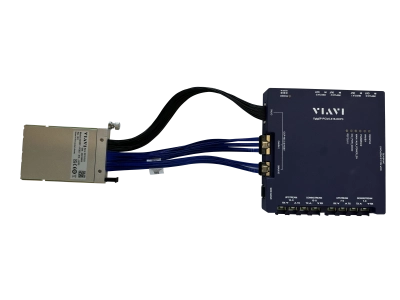

Xgig Exerciser Host Test Stand Interposer Module for PCI Express 5.0

The PCIe Exerciser Host Test Stand provides connectivity and power to a PCIe adapter card endpoint for testing and…

-

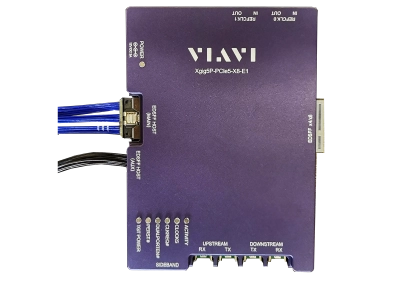

Xgig E1 EDSFF 8-Lane Interposer for PCI Express 5.0

The Xgig® 5P-PCIe5-X8-E1 Interposer is optimized for developing, debugging and performance-tuning NVMe SSD operation…

-

Xgig E3 EDSFF 16-Lane Interposer for PCI Express 5.0

The Xgig5P-PCIe5-X16-E3 Interposer is optimized for developing, debugging and performance-tuning NVMe SSD operation…

-

Xgig CEM 16-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 16-lane CEM Interposer enables debug and verification of new ICs, new system hardware designs, FPGA…

-

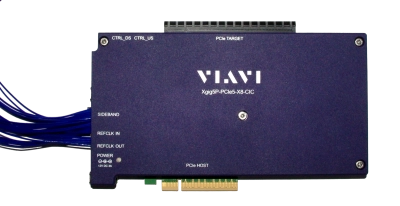

Xgig CEM 8-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 8-lane CEM Interposer enables debug and verification of new ICs, new system hardware designs, FPGA…

-

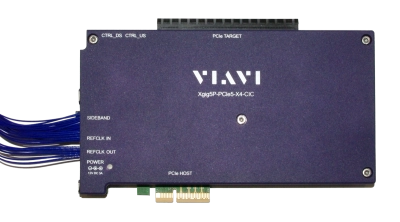

Xgig CEM 4-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 4-lane CEM Interposer enables debug and verification of new ICs, new system hardware designs, FPGA…

-

Xgig M.2 4-lane Interposer Module for PCI Express 5.0

The Xgig M.2, 4-lane Interposer for PCI Express® 5.0 is an Active Interposer with a design optimized for M.2 SSD…

-

Xgig U.2-Server, 4-lane Interposer Module for PCI Express 5.0

The Xgig® U.2-Server Interposer is optimized for development, debugging and tuning of NVMe SSD operation in high-…

-

Xgig U.3-Server, 4-lane Interposer Module for PCI Express 5.0

The Xgig® U.3-Server Interposer is optimized for development, debugging and tuning of NVMe SSD operation in high-…

-

Xgig Slimline 8-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 8-lane Slimline Interposer enables debug and verification of new ICs, new system hardware designs, FPGA…

-

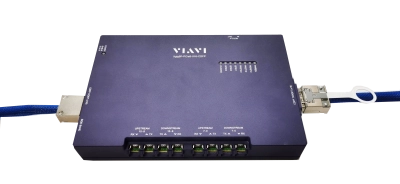

Xgig CDFP 16-lane Interposer for PCI Express 5.0

This PCIe 5.0 16-lane CDFP/CopprLink™ Interposer provides a tap of PCIe data signals between two externally cable-…

-

Xgig OCP3 16-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 16-lane OCP3 Interposer provides a tap of host-system PCIe signals to OCP NIC 3.0 devices for input…

-

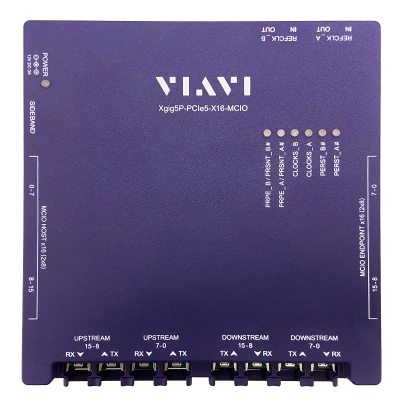

Xgig MCIO 16-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 16-lane MCIO/CopprLink™ Interposer enables protocol analysis of communication between a 16-lane MCIO/…

-

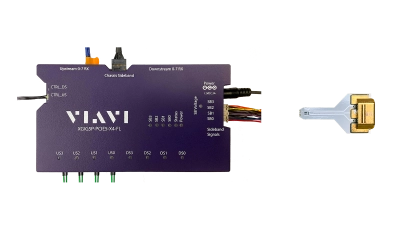

Xgig Flying Lead, 4-Lane Probe for PCI Express 5.0

Provides the data signal connection between a device under test and the VIAVI Protocol Analyzer chassis

-

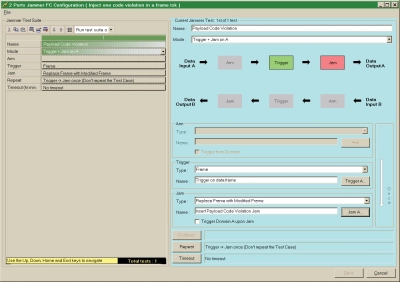

Xgig Jammer for PCI Express 5.0

The Xgig® Jammer manipulates live network traffic to simulate errors in real time, enabling users to verify the…

-

Xgig Exerciser for PCI Express 5.0

The PCIe Exerciser generates PCIe data streams and responses for compliance testing and analysis PCIe 5.0 protocol…

-

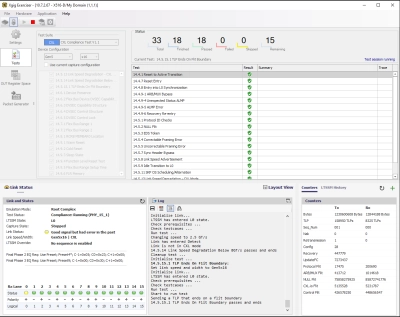

Xgig Exerciser for CXL v1.1/v2.0

Approved for CXL Gold Suite compliance testing, the CXL Exerciser generates CXL data streams and responses for…

-

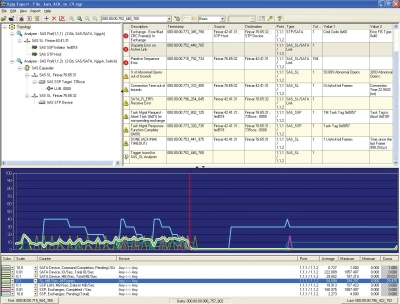

Xgig Expert

Expert software comes standard with all Xgig Analyzers to provide a unique and robust set of debugging and analysis…

-

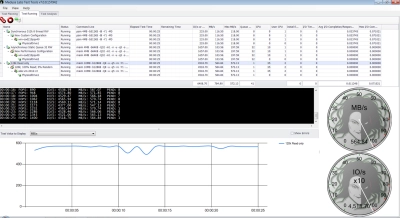

Medusa Labs Test Tools Suite

Medusa Labs Test Tools Suite is the leading application-based data testing and signal integrity testing tool…

Die PCIe-5.0-Plattform Xgig von VIAVI unterstützt im gleichen 5P16-Chassis sowohl Analyzer-, Exerciser- und Jammer-Funktionen als auch die Aufteilung des Analysator-Ports (Analyzer Port Bifurcation) sowie mehrere Nutzer gleichzeitig (Simultaneous Multi-User, SMU). Dieses multifunktionale Design kann dazu beitragen, die Anzahl der benötigten Geräte mit Einzelfunktionen zu verringern und daher die Anschaffungs- und Betriebskosten zu senken. Auch ermöglicht es eine höhere Produktivität der einzelnen Systeme für niedrigere Kosten-pro-Test/Kosten-pro-Nutzer sowie eine schnellere Fehlerbehebung (Debugging) für einen beschleunigten Marktauftritt.

Der Xgig Exerciser ist von der Peripheral Component Interconnect Special Interest Group (PCI-SIG) für Zertifizierungsprüfungen des PCI Express (PCIe) 4.0 Protokolls in PCI-SIG Compliance-Workshops zugelassen. PCIe 4.0 ist die höchste Ebene der Compliance-Zertifizierung, die aktuell von der PCI-SIG durchgeführt wird.

Was ist PCIe 5.0?

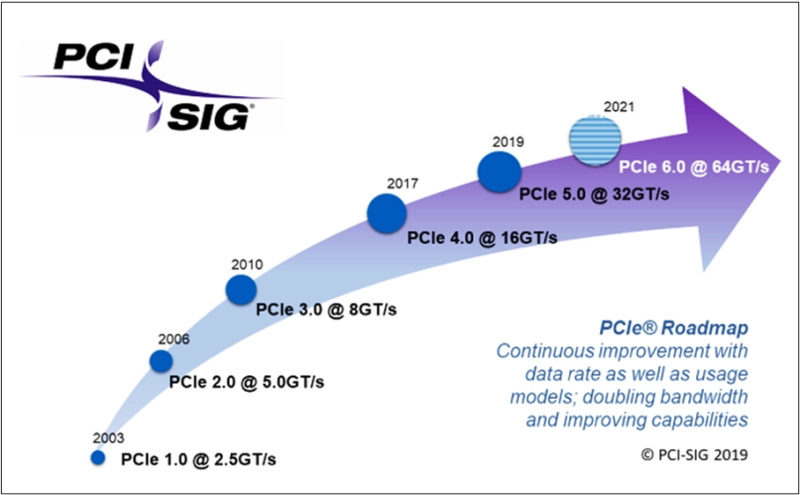

Die 5. Generation des Standards „Peripheral Component Interconnect Express“ ist als PCIe 5.0 bekannt. Weitere Bezeichnungen sind PCI Express 5.0, PCIe Gen-5 und PCIe5. Die erstmals 2003 eingeführte PCIe-Technologie hat sich zur Standardschnittstelle entwickelt, um Highspeed-Peripheriegeräte über einen separaten Punkt-zu-Punkt-Bus mit der CPU zu verbinden. Während es noch ganze sieben Jahre gedauert hatte, bis die Version PCIe 3.0 durch PCIe 4.0 ersetzt wurde, folgten die Entwicklung und Einführung der Spezifikationen von PCIe 5.0 bereits kurz nach PCIe 4.0 und ermöglichten erneut eine Verdoppelung der Bandbreite. Der endgültige PCIe-5.0-Standard ist bereits von der PCI-SIG veröffentlicht worden.

Angesichts der deutlichen Steigerung der Datenraten erhöhen sich mit jeder neuen PCIe-Version die an die Teststandards und -verfahren gestellten Anforderungen. PCIe 5.0 macht hier keine Ausnahme. Beispielsweise wirken sich überarbeitete EIEOS- (Electrical Idle Exit Ordered Set) und Takt-Funktionen auf die Vorgehensweise beim Testen sowohl der Geräte als auch der Systeme aus.

Zudem erlaubt die größere Vielseitigkeit jetzt anderen Protokollen, den bewährten Protokollstapel der PCIe-Bitübertragungsschicht (Physical Layer) zu nutzen, sodass Tests auch alternative Protokolle uneingeschränkt unterstützen müssen.

- Compute Express Link (CXL) ist ein von der Industrie gefördertes Cache-kohärentes Interconnect für Prozessoren, Erweiterungen (Expansion) und Beschleuniger (Accelerator).

- Das Protokoll NVM Express® (NVMe®) definiert, wie die Host-Software über mehrere Transportpfade, wie PCI Express® (PCIe®), RDMA und TCP, mit nichtflüchtigen Speichern (Non-Volatile Memory, NVM) kommuniziert. Dieses Protokoll gilt als Branchenstandard für Festkörperspeicher (SSD) in allen Formfaktoren (U.2, M.2, AIC, EDSFF).

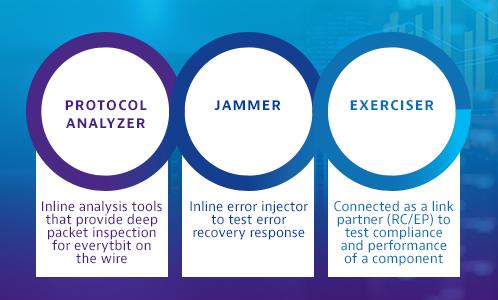

Xgig Analyzer

Uneingeschränkt abwärtskompatible Protokollanalysatoren, die eine Transferrate von 32 GT/s unterstützen, wie der VIAVI Xgig Analyzer, sind heute für das Testen und Debugging von PCIe 5.0 unverzichtbar. Ein größerer interner Speicher, mehr Speicherkapazität sowie die Segmentierung für die volumenintensivere Erfassung des Upstream- und Downstream-Verkehrs erlauben, längere Sequenzen aufzuzeichnen und dabei spezifische Pakete zur robusten Protokollanalyse herauszufiltern. Weitere Informationen zu Protokollanalysatoren finden Sie hier.

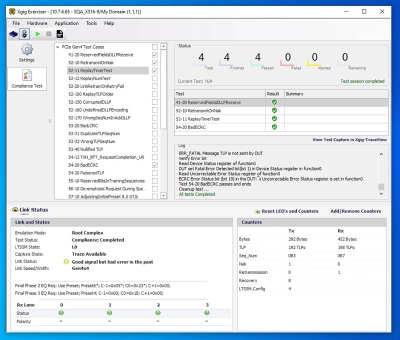

Xgig Exerciser

Der Xgig® Exerciser von VIAVI Solutions für PCIe 5.0 erweitert das Xgig-Produktportfolio um sofort nutzbare PCIe-Compliance-Tests.

- Unverzichtbarer Tester zum Debugging komplizierter Protokoll-Kommunikationsstörungen, da er die lückenlose und reproduzierbare Steuerung des PCIe-Datenverkehrs auf Bit-Ebene ermöglicht.

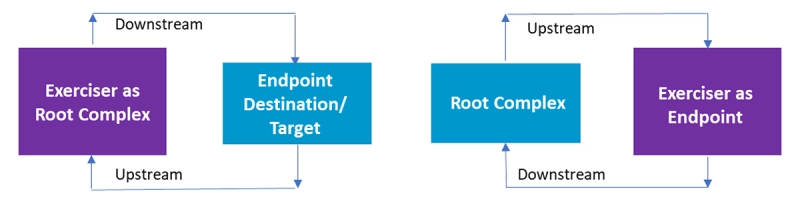

- Ersetzt den Partner der Kommunikationsverbindung (Link) und gewährleistet als Wurzel-Komplex (Root Complex, RC) oder als Endpunkt (Endpoint) die umfassende Kontrolle über die Tests (siehe Abbildung).

- Ideal zur Komponenten-Analyse und zum Debugging geeignet.

Exerciser können in zwei Betriebsmodi genutzt werden. Im Host- oder Root-Complex-Modus (links) werden Endpunkte getestet.

Der Endpunkt-Modus (rechts) erlaubt, Host-Systeme, Switch-Ports und CPUs zu überprüfen.

Der Xgig Exerciser ist von der Peripheral Component Interconnect Special Interest Group (PCI-SIG) für Zertifizierungsprüfungen des PCI Express (PCIe) 4.0 Protokolls in PCI-SIG Compliance-Workshops zugelassen. PCIe 4.0 ist die höchste Ebene der Compliance-Zertifizierung, die aktuell von der PCI-SIG durchgeführt wird. Weitere Informationen zu Exercisern und Generatoren finden Sie hier.

Xgig Jammer

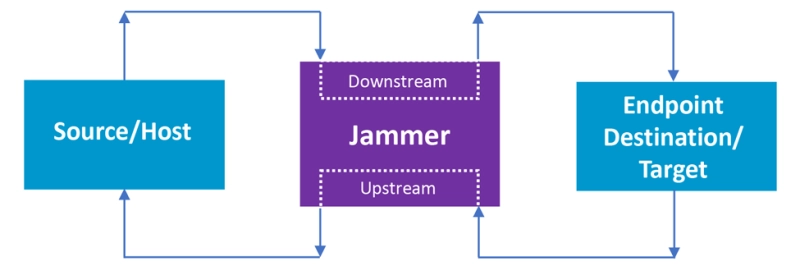

Jammer werden inline zwischen CPU und Endpunkten eingesetzt, um in die Kommunikation zwischen Systemgeräten bekannte Fehler einzufügen. Weitere Informationen zu Jammern finden Sie hier.

- Ideal zum Testen von Systemen und zur Analyse der Fehlerbehebung geeignet.

- Die Echtzeit-Simulation des Netzverkehrs ist ein kritisches Anforderungskriterium an die PCIe-Hardware.

- Trägt dazu bei, die spezifikationsgerechte Funktion der Geräte unter realen Einsatzbedingungen sicherzustellen.

- Unverzichtbar für einsatzkritische Produkte.

Interposer

Interposer ermöglichen, die Kommunikation zwischen einem Host-System und einem Prüfling (Device Under Test, DUT) aufzuzeichnen. VIAVI bietet eine lückenlose Palette gängiger PCIe-Interposer, wie:

- Host Test Stand

- CEM

- EDSFF, E1, E3

- U.2, U.3

- U.2 CEM

- M.2

- SFF-8674

- Flying-Lead

- Oculink Slimline

Xgig Tools Suite

Die PCIe-5.0-Plattform Xgig von VIAVI wird von der Xgig Tool Suite unterstützt, die die folgenden Komponenten umfasst:

- Xgig Expert™ ist eine bedienerfreundliche Benutzeroberfläche, die die Interpretation der Daten, die Fehlerdiagnose und die Leistungsanalyse beschleunigt.

- Xgig Serialytics™ basiert auf Xgig Expert und informiert über verborgene Verhaltensweisen und Ereignisse in einer Trace. Dieses Tool stärkt das kontextbasierte Debugging und stellt intelligente Analysen für serielle Protokolle zur Verfügung.

- Xgig Trace Control ist die Benutzeroberfläche für die Systemeinstellungen, mit deren Hilfe der Anwender das System für die Tests konfiguriert.

- Die Medusa Labs Test Tools Suite (MLTT) ist ein anwendungsbasiertes Tool zum Testen der Daten- und Signalintegrität, das den Entwicklern ermöglicht, Fehler durch Belastungstests zu identifizieren, zu lokalisieren und zu beheben.

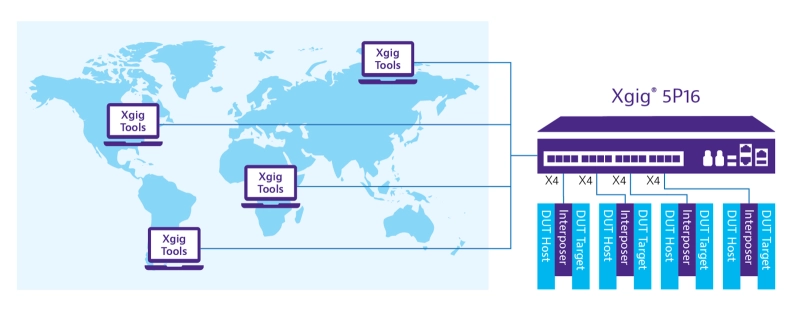

Bei der Protokollanalyse für PCI Express® führt ein Nutzer normalerweise einen einzelnen Test mit Spezialtechnik, die nur für eine einzige Funktion ausgelegt ist, durch. Mit der multifunktionalen Plattform können sich aber mehrere Nutzer gleichzeitig am gleichen Xgig® 5P16 oder 5P8 Analyzer anmelden und simultan eigenständige Tests ausführen.

PCIe Bifurcation zur flexiblen und simultanen Unterstützung mehrerer Nutzer (SMU)

Die Nutzer müssen sich auch nicht mehr am gleichen physischen Standort wie der Analyzer befinden. Sie können sich von jedem beliebigen Ort der Welt anmelden, vorausgesetzt sie haben Zugang zu einem Netzwerk. Die untenstehende Abbildung erläutert am Beispiel eines Analyzers mit 16 Lanes die Aufteilung (Bifurcation) in vier unabhängige Links, damit mehrere Nutzer gleichzeitig eigene Tests durchführen können.

Bei der „Bifurcation“ wird ein Port, der normalerweise einer logischen Verbindung (Link) entspricht, in mindestens zwei Links aufgeteilt. Wie in der Abbildung ersichtlich, kann ein Xgig 5P8 von VIAVI in zwei Links mit jeweils 4 Datenübertragungskanälen (Lanes) aufgeteilt werden, während ein Xgig 5P16 in zwei Links mit jeweils 8 Lanes oder in vier Links mit jeweils 4 Lanes aufteilbar ist.

Das Xgig 5P16 Chassis unterstützt auch Analyzer- Exerciser- und Jammer-Funktionen

Als das Flaggschiff von VIAVI bietet das Xgig 5P16 im gleichen Chassis alle Funktionen eines vollwertigen Analyzers, Exercisers und Jammers. Eine solche flexible, softwaredefinierte Plattform vereinfacht der Gerätemanagement deutlich. Software-Upgrades lassen sich schneller und wirtschaftlicher als Hardware-Module bereitstellen und können zudem jederzeit ergänzt werden. So werden die Manager in die Lage versetzt, ihr Budget zu schonen, bis das Upgrade benötigt wird.

Höhere Produktivität beschleunigt die Markteinführung und verringert Gesamteinsatzkosten (TCO)

Die multifunktionalen Xgig Analyzer ermöglichen effizientere Betriebsabläufe, die mit Geräten, die nur eine einzige Funktion unterstützen, nur schwer umsetzbar sind. Damit sind die Nutzer in der Lage, die Konfigurations- und Debugging-Prozesse zu rationalisieren, sodass die Produkte und Komponenten schneller getestet und schneller auf den Markt gebracht werden können.

Zugelassen für Zertifizierungsprüfungen gemäß PCI-SIG

Der Xgig Exerciser ist von der Peripheral Component Interconnect Special Interest Group (PCI-SIG) für Zertifizierungsprüfungen des PCI Express (PCIe) 4.0 Protokolls in PCI-SIG Compliance-Workshops zugelassen. PCIe 4.0 ist die höchste Ebene der Compliance-Zertifizierung, die aktuell von der PCI-SIG durchgeführt wird. VIAVI arbeitet aktiv in der PCI-SIG mit, um PCIe 5.0 Compliance-Prüfungen zu ermöglichen.

Das 2019 veröffentlichte endgültige Release des Standards PCI Express 5.0 kennzeichnet den Höhepunkt eines 18 Monate andauernden, beschleunigten Entwicklungszyklus, der als notwendig erachtet wurde, um den eskalierenden Leistungsbedarf datenintensiver Anwendungen zu berücksichtigen.

Wie alle früheren Generationen ist auch bei PCIe 5.0 die Abwärtskompatibilität gewährleistet, wobei die jeweils niedrigere Version weiterhin maßgeblich für die Transferrate zwischen PCIe-Slot und Anschlusskarte bleibt. Neben der größeren Bandbreite enthalten die neuen Spezifikationen auch Überarbeitungen auf der elektrischen Ebene zur Verbesserung der Signalintegrität sowie neue Kriterien zur Optimierung der mechanischen Leistung der Steckverbindungen.

Wie schon bei allen vorhergehenden Generationen stellt auch die Abwärtskompatibilität der aktuellen Version PCIe 5.0 sicher, dass die anspruchsvollsten und leistungsstärksten Anwendungen, wie Cloud-Computing und Künstliche Intelligenz (KI), die Vorteile der größten verfügbaren Transferrate nutzen können, während frühere Technologie-Generationen weiter für weniger anspruchsvolle Anwendungen verfügbar bleiben.

Die Verabschiedung des Standards PCIe 5.0 im Jahr 2019 war der erste von vielen Schritten auf dem Weg zur Implementierung dieser neuen Technologie-Generation. Auch sind noch vorläufige Konformitäts- und Interoperabilitätsprüfungen abzuschließen. Diese zusätzlichen Meilensteine könnten die Einführung der ersten zertifizierten kommerziellen Produktangebote für PCIe 5.0 weiter hinauszögern.

Da die PCIe-Technologie heute in nahezu alle Arten von Rechnersystemen integriert ist, gehören viele der weltweit größten Unternehmen aus den Bereichen Elektronik, Computing, Datenspeicher und E-Commerce der symbiotischen Infrastruktur der Kunden- und Lieferkette für PCIe 5.0 an. Dazu zählen beispielsweise IP-Lieferanten von geistigem Eigentum (Intellectual Property, IP), die die Funktionalität von PCIe 5.0 ermöglichen, Switch- und Retimer-Hersteller sowie Zulieferer von Mainboards, Speichergeräten und Grafik-Controllern für PCIe 5.0. Diese wichtigen Komponenten sind Bestandteil der anspruchsvollen Computersysteme und Geräte, die für Rechenzentren und andere wichtige Netzwerkinstallationen benötigt werden.

Marktsegmente mit frühzeitiger Einführung von PCIe 5.0

Es wird nicht davon ausgegangen, dass alle Unternehmen und Marktsegmente sofort PCIe 5.0 einführen werden. Die IP-Märkte sind auf frühzeitige Validierungsmöglichkeiten angewiesen, um die Funktionalität im FPGA-/Halbleiter-Format sicherzustellen. Auch CPU-, Ethernet- und ausgewählte Accelerator-Anbieter werden bei der frühzeitigen Einführung von PCIe 5.0 eine wichtige Rolle spielen. Server in Rechenzentren sowie High-Performance-Computing(HPC)-Infrastrukturen, die bereits mit den sich verschärfenden Bandbreiten- und Latenzforderungen zu kämpfen haben, werden schnell von den Vorteilen der PCIe-5.0-Technologie profitieren wollen.

Anwender der PCIe-5.0-Protokollanalyse

Um eine schnellere Markteinführung sicherzustellen, müssen die Validierungs- und Debugging-Zyklen beschleunigt werden. Das erhöht die Nachfrage nach anspruchsvollen Protokollanalysatoren durch Integrationsteams, die für die Verifizierung und Validierung der Systeme verantwortlich sind, sowie durch Debugging-Teams, die mit der Qualifizierung der Komponenten und Behebung von Interoperabilitätsproblemen betraut sind. Auch Anwender, die das Performance-Tuning der Geräte, Treiber und Anwendungssoftware sicherstellen, werden aus ihrer Investition in anspruchsvolle Protokollanalysatoren für PCIe 5.0 eine erhebliche Rendite erwirtschaften.

Auch mit der fünften Generation der PCIe-Technologie hat sich die Transferrate wie bei allen Vorgängern weiter verdoppelt. Mit der gleichen 128b/130b-Codierung, die seit Version PCIe 3.0 Standard ist, stellt PCIe 5.0 jetzt in jeder Richtung einen Durchsatz von 64 GB/s zur Verfügung. Da die PCIe-Technologie vollduplexfähig ist, werden in beiden Richtungen zusammengenommen maximal 128 GB/s übertragen.

Bis PCIe 2.1 wurde ein 8b/10b-Leitungscode verwendet, das heißt, acht Datenbit wurden in einem 10 Bit langen Codewort übertragen. Das hatte bei der Leistung einen nicht nutzbaren Overhead von 20 % zur Folge, der die Brutto-Transferrate von 2,5 GT/s auf eine Nettobandbreite von nur 2,0 Gbit/s verringerte. Mit der ab PCIe 3.0 genutzten 128b/130b-Codierung wird dagegen auch bei PCIe 5.0 ein effizienterer Overhead-Faktor von 1,5 % beibehalten.

|

PCIe-Version |

Release Jahr |

Transferrate |

Durchsatz/Lane |

x16-Durchsatz |

|

1.0 |

2003 |

2,5 GT/s |

250 MB/s |

4,0 GB/s |

|

2.0 |

2007 |

5 GT/s |

500 MB/s |

8,0 GB/s |

|

3.0 |

2010 |

8,0 GT/s |

1,0 GB/s |

16,0 GB/s |

|

4.0 |

2017 |

16,0 GT/s |

2,0 GB/s |

32,0 GB/s |

|

5.0 |

2019 |

32,0 GT/s |

4,0 GB/s |

64,0 GB/s |

Diese beeindruckende Geschwindigkeit von PCIe 5.0 würde es beispielsweise erlauben, den Inhalt einer typischen Blu-Ray-Disk in weniger als einer Sekunde in den nichtflüchtigen Speicher (NVM) eines PCIe-5.0-Mainboards zu übertragen. Obgleich eine solche Datenrate auf den ersten Blick übertrieben erscheinen mag, ist sie doch durch die in anderen Bereichen erfolgten Weiterentwicklungen in der Netzarchitektur notwendig geworden. Beispielsweise erfordert 400G Ethernet in jeder Übertragungsrichtung eine Bandbreite von 50 GB/s, um mit maximaler Kapazität an den Hauptprozessor (CPU) angeschlossen zu werden.

Bei PCIe 4.0 erwiesen sich die 32 GB/s, die ein vollwertiger x16-Slot zur Verfügung stellt, als unzureichend. Die von PCIe 5.0 gebotene Bandbreite übersteigt den Bedarf dieser Schnittstelle dagegen und lässt sogar noch etwas Reserve.

Doch nicht nur Ethernet-Netze treiben die Entwicklungszyklen voran. Eine wichtige Rolle spielen auch die neuen Echtzeitsysteme mit latenzkritischen Leistungsanforderungen, wie autonomes Fahren, Verteidigungsanwendungen, die eine sofortige Reaktion erfordern, sowie kritische Anwendungen im Bereich der Finanzsicherheit, bei denen Hacking-Versuche umgehend abgewehrt werden müssen. Einzelne Nutzer von Multi-GPU-Systemen und Premium-Grafikkarten profitieren ebenfalls erheblich von der größeren Transferrate und Bandbreite bei PCIe 5.0.

Die Spezifikation von PCIe 5.0 kann als natürliche Weiterentwicklung des abwärtskompatiblen PCIe-Standards angesehen werden, wobei in dieser Version keine Änderungen an der Datensicherungsschicht (Data Link Layer, DLL) und Transaktionsschicht (Transaction Layer, TL) vorgenommen wurden. Auch profitiert diese Spezifikation weiterhin von der skalierbaren Flusssteuerung und den erweiterten Tags und Credits, die mit PCIe 4.0 eingeführt wurden.

Ebenfalls ergänzt wurde ein neuer CEM-Steckverbinder für Add-in-Karten (AIC). Verbesserungen an der Signalintegrität und am Design der Steckverbindung haben die Leistung und Zuverlässigkeit insgesamt gesteigert. Auf der Bitübertragungsschicht wurden Verbesserungen an den „Ordered Sets“ von EIEOS und SKP sowie an den Entzerrungssequenzen (EQ) eingeführt.

Bei den Hardware-Herstellern und Branchen-Insidern ist die Spezifikation von PCIe 5.0 im Allgemeinen auf ein positives Echo gestoßen. Insbesondere die Erweiterungen zur Verbesserung der Testfähigkeit, zum schnelleren Link-Training sowie zur Unterstützung alternativer Protokolle werden als äußerst vorteilhaft angesehen. Dieser Konsens in der Industrie in Verbindung mit den relativ niedrigen Hürden für den Übergang von 4.0 auf 5.0 haben dazu geführt, dass für die Hardware offensive Entwicklungs- und Kommerzialisierungsziele formuliert wurden.

Die Fortschritte und Spezifikationsänderungen des neuen Standards PCIe 5.0 haben viele der Herausforderungen, die in der PCIe-Architektur begründet sind und die die Testausführung und die Entwicklungsmaßnahmen verkomplizieren, weiter verschärft. Dazu gehört die Forderung nach einer 2-fachen Verringerung des Sender-Jitters (Tx) und einer 3-fachen Verringerung des Referenztakt-Jitters.

Auch bei PCIe 5.0 bleibt die Signaldämpfung eine wichtige architekturbasierte Herausforderung. Retimer, Redriver und alternative Basismaterialien für Leiterplatten gehören zu den optionalen Kostenvorteilen, die Hardware-Entwicklern zur Verfügung stehen, um die Auswirkungen dieser Vorgaben abzumildern. Ein Retimer wird genutzt, um das gleiche Signal erneut zu übertragen, während ein Redriver das Signal lediglich verstärkt. Diese Funktionen verbessern die physische Reichweite der logischen Verbindung (Link).

Die Spezifikation von PCIe 5.0 legt für die Kanaldämpfung ein Budget von 36 dB fest, das damit nur etwa 28 % über dem Schwellwert von PCIe 4.0 liegt. Die mit der PCIe-Technologie verbundene Einfügedämpfung bleibt auch bei PCIe 5.0 ein Thema. Die Dämpfungspegel des Leiterplattenmaterials FR4 sind nicht länger akzeptabel und alternative Materialien, wie MEGTRON, die bis zu 2,5-mal mehr kosten, sind obligatorisch geworden. Auch haben die von PCIe 5.0 an die Kanäle gestellten Anforderungen neue Entzerrungsschaltungen für Sender (Tx) und Empfänger (Rx) notwendig gemacht. Zudem ist die Ausnutzung der elektrischen Reserve am Empfänger („Lane-Margining“) bei Spannung und Taktung unverzichtbar geworden.

Beim Übergang von PCIe 4.0 zu PCIe 5.0 hat sich die Implementierungsstrategie auf die Verdopplung der Transferrate, die Abwärtskompatibilität und einen kürzeren Release-Zyklus konzentriert.

Neue Leistungsmerkmale, die den Geschwindigkeitszuwachs ermöglichten oder förderten, hatten Vorrang vor anderen empfohlenen oder gewünschten Änderungen. Beispielsweise mussten der EIEOS-Satz und die Definition der Datenbitrate überarbeitet werden, um die Transferrate zu erhöhen. Grundlegende PCIe-Elemente, wie die Codierung und der Schwellwert der Bitfehlerrate (BER), wurden dagegen nicht verändert. Auch die Signalisierungs- und Scrambling-Verfahren sind mit denen von PCIe 4.0 identisch und man übernahm die bestehenden Rx-/Tx-Testmethoden, um die Implementierung zu vereinfachen.

Obwohl der Schwerpunkt auf eine frühe Markteinführung und auf die Kompatibilität gelegt wurde, gibt es bei PCIe 5.0 doch Design-Änderungen, die sich notwendigerweise auf die Steckverbindung und die Testverfahren auswirken. Dazu gehören die Taktrückgewinnung (CDR) mit einer Antwort zweiter Ordnung sowie ein CEM-Verbinder, der nur zu einem oberflächenmontierten (SMT) PCB-Footprint kompatibel ist, aber an der Add-in-Karte abwärtskompatibel bleibt. Über modifizierte TS1-/TS2-Trainingssequenzen unterstützt PCIe 5.0 nun auch alternative Protokolle.

Bedingt durch die ungewöhnlich lange Entwicklungszeit von PCIe 4.0 war auch deshalb eine größere Übereinstimmung mit der nächsten Generation PCIe 5.0 erforderlich, weil sich die Netzwerke und die Bandbreitennachfrage natürlich weiterentwickelt hatten. Aufgrund der dadurch entstehenden zeitlichen Überlappung beider Standards waren übereinstimmende Design- und Testverfahren für einen reibungslosen Übergang praktisch unverzichtbar.

Aktualisierung der Bitübertragungsschicht bei PCIe 5.0

Wie oben bereits erwähnt, führt PCIe 5.0 strengere Jitter-Spezifikationen, anspruchsvollere Budgetvorgaben für die Kanaldämpfung sowie neue Anforderungen an das Lane-Margening (Spannung, Taktung) ein. Zudem waren aufgrund der höheren Transferrate Änderungen an der Bitübertragungsschicht (Physical Layer) erforderlich. Weitere technische Neuerungen sichern die Abwärtskompatibilität zu früheren PCIe-Generationen.

Die Spezifikation von PCIe 5.0 enthält auch wichtige Änderungen am Ordered Set. Das „Electrical Idle Exit Ordered Set“ (EIEOS) wird genutzt, um den elektrischen Ruhezustand (Idle State) zu verlassen. Das vom „Ordered Pair“ bei PCIe 4.0 her bekannte Muster aus 16 Nullen und Einsen vergrößerte sich bei PCIe 5.0 auf 32 Nullen und Einsen, die für jede Lane wiederholt werden. Die (wiederholten) Back-to-Back-EIEOS-Signale kennzeichnen eine weitere Protokolländerung. Auch der „Start of Data Stream Ordered Set“ (SDS) wurde aktualisiert, sodass der Empfänger die Ursprungspunkte des Datenstroms jetzt eindeutig unterscheiden kann.

Die Trainingssequenzen (TS1/TS2) profitieren von neuen innovativen Optionen, die die Verdoppelung der Transferrate von PCIe 5.0 vereinfachen sollen. Sie sind nun eine notwendige Vorstufe für den Link-Aufbau und die Entzerrung (EQ). Allerdings können sie auch Verzögerungen verursachen, da die Ordered Sets alle unterstützten Datenraten-Stufen, beginnend bei 2,5 GT/s schrittweise bis zur Transferrate von 32,0 GT/s von PCIe 5.0, durchlaufen. Um dieses Problem zu vermeiden, sind EQ-Bypass-Optionen vorgesehen, die die Entzerrung der Datenraten-Zwischenstufen umgehen. Es ist auch möglich, die Entzerrung durch Auswahl der „No EQ“-Option insgesamt auszulassen, sodass sofort zum aktiven Datentransfer-Status L0 übergegangen wird.

Weiterhin besitzen die modifizierten TS1-/TS2-Sequenzen von PCIe 5.0 neue Felder für die Kennungen (ID) alternativer Protokolle und bieten eine erweiterte Unterstützung der Vorcodierung. Nach erfolgreicher Aushandlung der Parameter (Negotiation) zwischen dem System und dem betreffenden Gerät, kann der Link dann sofort mit der höchsten unterstützten Datenrate in den L0-Status übergehen und die Übertragung mit dem ausgehandelten alternativen Protokoll einleiten. Sollte es nicht möglich sein, ein alternatives Protokoll auszuhandeln, kehrt das System umgehend zum Standardprotokoll von PCIe 5.0 zurück.

Bei PCIe 5.0 erschwert eine nahezu grenzenlose Vielfalt von Link-Bedingungen und -Szenarien die Fehlerdiagnose in der Aufbauphase (Pre-L0) und in der Betriebsphase (L0) der Link-Aktivität. Die besten Testlösungen für PCIe 5.0 bieten ein schichtenweises, systematisches Testkonzept an, das den Arbeits- und Zeitaufwand für die Fehlerdiagnose und -behebung deutlich verringert und gleichzeitig die Kennwerte der Systemleistung verbessert.

Typische Probleme während des Link-Aufbaus (Bring-up-Phase), hier insbesondere beim Link-Training und Statusübergang (Link Training and Status State Machine, LTSSM) betreffen die Signalintegrität und die Geräteerkennung, falsche Link-Raten sowie weitere potenzielle Störungen, die mit einem Protokollanalysator effektiv untersucht werden können. Mithilfe eines modernen PCIe-Protokollanalysators ist es nach Erreichen des L0-Status möglich, Leistungsmängel, wie übermäßige Übertragungswiederholungen (Replay), Rückgewinnungsprobleme und Verzögerungen auf den verschiedenen Schichten des Protokollstapels effizient zu erkennen und abzuschwächen.

Ein häufiger Fehler auf der PHY-Layer, der eine präzise Diagnostik erfordert, führt beim Verlassen des elektrischen Ruhezustands (Electrical Idle, EI) zu Fehlanpassungen zwischen der Tx- und Rx-Logik, die die Latenz vergrößern. Der VIAVI Xgig Analyzer erkennt diese Störungen zuverlässig, da er kurze Synchronisationszeiten mit anspruchsvollen Nachbearbeitungsfunktionen kombiniert, sodass aufgezeichnete Daten während der Übergänge vom Low-Power-Status kaum noch verloren gehen.

Bei der Überwachung des allgemeinen Signalstatus und der Rückgewinnungsdaten der Links spielen Echtzeitwerte für die Bitübertragungsschicht eine sehr große Rolle. Wenn sich der Link beispielsweise im Betriebsstatus L0 befindet, werden Übertragungswiederholungen und Datenrückgewinnungen, die die Systemleistung deutlich beeinträchtigen können, häufig nicht erkannt. Die Echtzeit-Überwachung des Xgig Analyzer mit seinen praktischen Kennwerten und der Analyse des für jede einzelne Lane aufgezeichneten Verkehrs ermöglicht die effektive Überwachung und Diagnose von negativen Empfangsbestätigungen (NAK), Übertragungswiederholungen, Link-Fehlern und der Flusssteuerungsstatistik, wie einen Pufferüberlauf beim Empfänger und eine zu große Warteschlangentiefe für Transaktionen.

Es sieht ganz so aus, als ob das rasante PCIe-Release-Tempo weiter anhalten wird, denn bereits 2021 wird die Veröffentlichung der endgültigen Spezifikation von PCIe 6.0 erwartet. Diese neue Version wird die schon traditionelle und für den PCIe-Standard typische Verdopplung der Bandbreite und die Abwärtskompatibilität beibehalten sowie in beiden Richtungen eine Transferrate von beeindruckenden 256 GB/s erreichen. Damit zieht PCIe mit der VRAM-Bandbreite preiswerter Grafikprozessoren (GPU) gleich.

Um bei identischer Zuverlässigkeit eine weitere Verdoppelung der Übertragungsrate zu ermöglichen, müssen die Pulsamplituden-Modulation (PAM-4) und die Vorwärtsfehlerkorrektur (FEC) einbezogen werden. Davon könnten die künstliche Intelligenz (KI) und das maschinelle Lernen (ML) profitieren, da deren Leistung von einer Kombination aus sehr hoher Datenrate, geringer Latenz und schnellem simultanen Zugriff auf mehrere Peripheriegeräte abhängig ist.

PCIe 5.0 kennzeichnet einen weiteren Entwicklungssprung in der E/A-Bus-Technologie. Es scheint, dass die Spezifikation von PCIe 5.0 mit dem Mooreschen Gesetz Schritt halten und gleichzeitig auf absehbare Zeit den Engpass in der Netzarchitektur überwinden kann. Mit den verbesserten Testern für PCIe 5.0, die jeden Tag neu auf den Markt kommen, sollten sich diese Fortschritte über PCIe 6.0 hinaus für viele zukünftige Generationen dieser Technologie weiter fortsetzen.

Wir stehen Ihnen immer zur Seite

Bei uns erhalten Sie den Support, die Services, die umfassenden Schulungen und die Ressourcen, die Sie benötigen. Diese Leistungen tragen zur Maximierung Ihrer VIAVI Investitionen bei.

Fragen Sie einen Experten

Wenden Sie sich an uns, wenn Sie mehr Informationen oder ein Preisangebot wünschen. Bei uns finden Sie die Experten, die alle Ihre Fragen beantworten können.