Mess- und Prüftechnik für PCIe

Detaillierte Analyse der Kommunikation auf allen Schichten des PCIe-Stapels

Jede neue, bestätigte Version von PCIe hat die Datenrate und Bandbreite verdoppelt. Damit wurden die benötigten PCIe-Tests immer anspruchsvoller, da die Aufzeichnung, Speicherung und Visualisierung der Daten an Komplexität gewannen. Seit der Einführung der ersten PCIe-Generation im Jahr 2003 ist die entsprechende Prüf- und Messtechnik kontinuierlich an die neuen Anforderungen angepasst und verbessert worden. Heute steht eine lückenlose Palette an Testern zur Verfügung, die effiziente und präzise Fehlerdiagnosen und Messungen an PCI-Express-Hardware ermöglicht.

Einführung in PCIe (Peripheral Component Interconnect Express)

„Peripheral Component Interconnect Express“, abgekürzt „PCI Express“, „PCI-E“ oder wie in diesem Artikel „PCIe“, ist eine leistungsstarke Bus-Architektur für den Computer, die für die Verbindung nahezu aller internen Computerkomponenten zum Branchenstandard geworden ist.

PCIe stellt die Verbindungen zwischen Prozessoren und Speichern des Computers zu anderen Komponenten und Peripheriegeräten her. Diese Schnittstelle gewährleistet die serielle Highspeed-Datenübertragung und wurde entwickelt, um ältere parallele Bus-Architekturen, wie PCI und ISA (Industry Standard Architecture), abzulösen. PCIe nutzt einen Bus mit Punkt-zu-Punkt-Verbindungen, der gegenüber den Vorgängersystemen eine weitaus höhere Datenübertragungsrate gewährleistet.

In den 1980er-Jahren basierte die Bus-Architektur der ersten Computer auf parallelen Datenpfaden, die den Hauptprozessor (CPU) mit allen Komponenten verbanden.

Ende der 1990er-Jahre wurden die Vorgänger von PCIe entwickelt. Sie integrierten den vertrauten Formfaktor der Geräte-Steckkarten in die entsprechenden Steckplätze (Slot) auf der Hauptplatine (Mainboard). Der PCI-Bus stand in 32- und 64-Bit-Ausführungen zur Verfügung, während der AGP-Anschluss (Accelerated Graphics Port) speziell für den Grafik-Controller entwickelt wurde, der eine größere Bandbreite benötigte, als der PCI-Bus bereitstellen konnte. Heute werden beide Schnittstellen größtenteils durch PCIe ersetzt.

Anfang der 2000er-Jahre hatte der rasant wachsende Bedarf der internen Hardware und der Peripheriegeräte an Rechenleistung zur Entwicklung der nächsten PCI-Generation, die als PCI Express, PCI-E oder PCIe bezeichnet wurde, geführt. Der größte Vorteil von PCIe gegenüber dem konventionellen PCI besteht darin, dass die neue Architektur auf eine parallele Schnittstelle, wie bei PCI, verzichtet und stattdessen eine serielle Schnittstelle verwendet. Ein weiterer Vorteil ist, dass PCIe kein geteiltes (shared) Bus-System nutzt, sondern zu jedem angeschlossenen Gerät eine separate Punkt-zu-Punkt-Verbindung herstellt.

Durch die Bereitstellung mehrerer Datenübertragungskanäle (Lanes) zu den angeschlossenen Geräten konnte die Übertragungsrate weiter erhöht werden. In Abhängigkeit von der Anzahl der zugewiesenen Datenport-Anschlüsse bewirkt jede weitere Lane eine entsprechende Erhöhung des Datenübertragungsvolumens, d. h. x1 (um 1) bis zu x16 (um das 16-Fache). Damit war es möglich, die Daten von Punkt A zu Punkt B gleichzeitig auf mehreren Datenpfaden zu übertragen, wenn die benötigte Kapazität es erforderte.

Mit der zunehmenden Verbreitung und Beliebtheit von PCIe als De-facto-Standard ist diese Schnittstelle von einer Vielzahl von Funktionskomponenten wie USB, Bluetooth-Produkten und Videokarten, übernommen worden. Video-Controller und Speichergeräte sind Beispiele für Technologien, die mit der Einführung der PCIe-Architektur erst möglich wurden. Das zeigt sich an der Grafikdarstellung und Computerleistung, die sich in den vergangenen zehn Jahren deutlich verbessert haben.

Die mit der Architektur der PCIe-Versionen verbundenen technischen Meilensteine haben deutlich höhere Datenübertragungsraten als beim PCI-Bus ermöglicht. Jede neue Version hat diesen Trend weiter verstärkt. Während die herkömmliche PCI-Architektur gemeinsame Adress-, Daten- und Kommando-Leitungen nutzte, stellt die Punkt-zu-Punkt-Topologie von PCIe jedem angeschlossenen Gerät separate Verbindungen zur Verfügung. Dadurch wird es durch eventuelle Leistungsbeschränkungen anderer Komponenten nicht beeinträchtigt.

Die PCIe-Verbindung teilt die Datenübertragung in Pakete auf. Hierbei kommt der Transaktionsschicht des PCIe-Ports die Aufgabe zu, die Paketierung und De-Paketierung der Daten auszuführen. Dieser Unterschied in der elektrischen Signalisierung von PCIe gegenüber dem konventionellen PCI erforderte einen vollkommen neuen Aufbau der Elektronik und Steckverbindungen, sodass PCIe-Slots nicht für PCI-Karten nutzbar sind.

Für PCIe wurden mehrere unterschiedliche Formate mit leicht unterschiedlichen Bezeichnungen entwickelt. Jeder Anwender sollte die Abmessungen und Versionen dieser PCIe-Formate kennen. Dieses Wissen ist die Voraussetzung, um zu verstehen, welche Erweiterungskarten in dem vorhandenen System nutzbar sind.

PCIe-Versionen

Seit der Einführung von PCIe 1.0 im Jahr 2002 sind nacheinander weitere Releases veröffentlicht worden, um der wachsenden Nachfrage nach mehr Bandbreite und höheren Datenraten gerecht zu werden. Die Version 1.0 stellte für den Verkehr auf 16 kombinierten Lanes eine Bandbreite von knapp 8 GB/s zur Verfügung, während die Übertragungsrate (Schrittgeschwindigkeit) 2,5 Gigatransfer/Sekunde (GT/s) betrug. Mit jedem neuen Release hat sich die Gesamtbandbreite verdoppelt, sodass mit der Einführung von PCIe 5.0 im Jahr 2019 dann eine Bandbreite von 128 GB/s zur Verfügung stand. Gleichzeitig hat sich die Übertragungsrate schrittweise von 2,5 GT/s auf 32,0 GT/s erhöht. Neben den Leistungsverbesserungen stellt jede neue Version auch neue Funktionen und eine höhere Energieeffizienz zu Verfügung.

Das anspruchsvolle Vorhaben, im Abstand weniger Jahre die Bandbreite zu verdoppeln, damit der PCI-Bus nicht zum Engpass wird, da die Prozessorgeschwindigkeit und der Speicher sich rasant weiterentwickeln, stellt die Produktdesigner immer wieder vor neue Herausforderungen. Mit der Bandbreite steigt auch das Risiko möglicher Störungen durch Nebensprechen und elektrische Unterbrechungen. Daher dringt man mit den Materialien und Design-Innovationen immer wieder bis an die Grenzen des technisch Machbaren vor.

PCIe-Größen

Die Abmessungen der PCIe-Karte sowie die Anzahl der Steckkontakte (Pins) sind durch die Anzahl der Lanes und Verbindungen vorgegeben. Das gilt für alle PCIe-Versionen. Heute stehen die folgenden PCIe-Größen mit der entsprechenden Pin-Anzahl zur Verfügung:

| Typ | Länge | Pin-Anzahl |

| PCI Express x1 | 25 mm | 18 |

| PCI Express x4 | 39 mm | 32 |

| PCI Express x8 | 56 mm | 49 |

| PCI Express x16 | 89 mm | 82 |

Im Unterschied zu PCI kann eine PCIe-Karte in einen beliebig langen PCIe-Steckplatz gesteckt werden, der nur nicht kürzer sein darf. Das bedeutet, dass eine x1-Karte für einen x1-, x4-, x8- oder x16-Slot genutzt werden kann. Im Umkehrschluss heißt das, dass eine x16-Karte beispielsweise in einen x4-Slot gesteckt werden kann, doch nur wenn dieser Slot als „offener“ Steckplatz ohne abschließenden Steg konfiguriert ist. In diesem Fall wäre die Bandbreite jedoch auf die Kapazität einer x4-Karte begrenzt.

Die der PCIe-Karte zur Verfügung gestellte Bandbreite ist vom CPU bzw. dem Controller auf dem Mainboard abhängig. Das bedeutet, dass eine 5.0-Karte nur mit der Bandbreite einer 4.0-Karte betrieben wird, wenn der Controller für die Version 4.0 konfiguriert wurde.

Während die erste Version PCIe 1.0 nur eine Bandbreite von 8 GB/s zur Verfügung stellte, hat sich die Datenrate mit jeder weiteren Version bis PCIe 5.0 auf 128 GB/s, die über 16 Lanes übertragen werden, erhöht. Allerdings steigt mit der Bandbreite auch das Risiko möglicher Störungen durch Nebensprechen und elektrische Unterbrechungen. Daher sind die jüngsten Innovationen beim Leiterplattenmaterial und zur Ausnutzung der elektrischen Reserve am Empfänger („Lane-Margining“) eine Voraussetzung, um dieser rasanten Entwicklung gerecht zu werden. Ein weiteres wichtiges Kriterium ist die technische Vielseitigkeit des PCIe-Formats. Da großen Wert auf die Austauschbarkeit gelegt wird, müssen die Entwickler sowohl von Prüf- und Messtechnik als auch von Produkten für diese Technologie diese Anforderung in ihrer Arbeit berücksichtigen. Die Abwärtskompatibilität zwischen den PCIe-Versionen bleibt ein wesentlicher Faktor. Slot-Größen von x1 bis x16 unterstützen die PCIe-Karten jeder Größe, wobei der jeweils kleinere Wert die verfügbare Bandbreite definiert

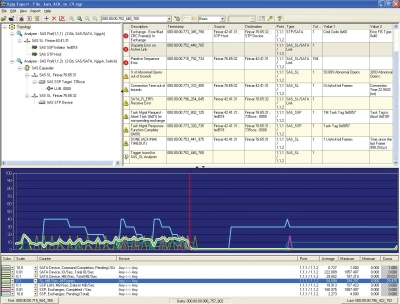

PCIe und NVMe

„Non-Volatile Memory Express“ (NVMe) ist ein SSD-Protokoll, das speziell entwickelt wurde, um nichtflüchtige Massenspeicher (NVM) über PCIe zu verbinden. „Nichtflüchtig“ bedeutet in diesem Fall, dass die Daten auch ohne Stromversorgung im Speicher erhalten bleiben. NVMe nutzt die vorteilhafte PCIe-Architektur, um Lese- und Schreibgeschwindigkeiten von mehr als dem Doppelten einer SAS-Schnittstelle (12 Gbit/s) zu erreichen. Anstatt einen konventionellen I/O-Controller zu verwenden, wird NVMe über PCIe direkt mit dem Hauptprozessor (CPU) verbunden. Um diese PCIe-NVMe-Kombination effektiv testen zu können, werden Tester mit einer sehr großen Speicherkapazität und mit Segmentierungsfunktion benötigt. Nur so ist es möglich, den NVMe-Verkehr präzise zu decodieren.

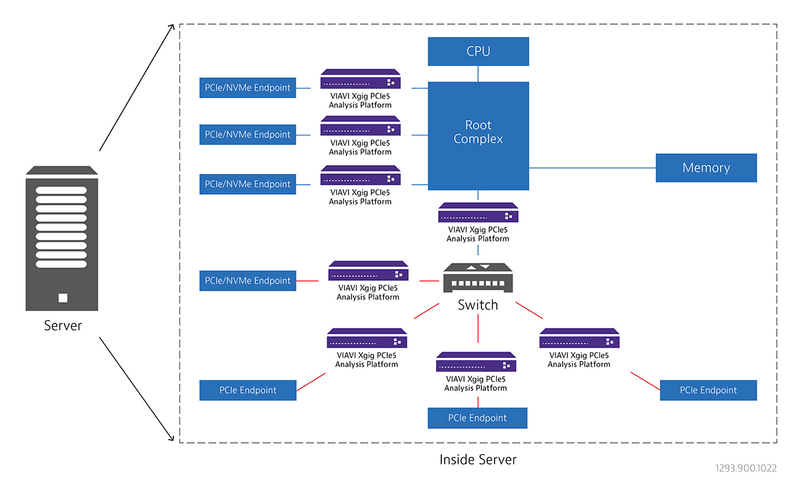

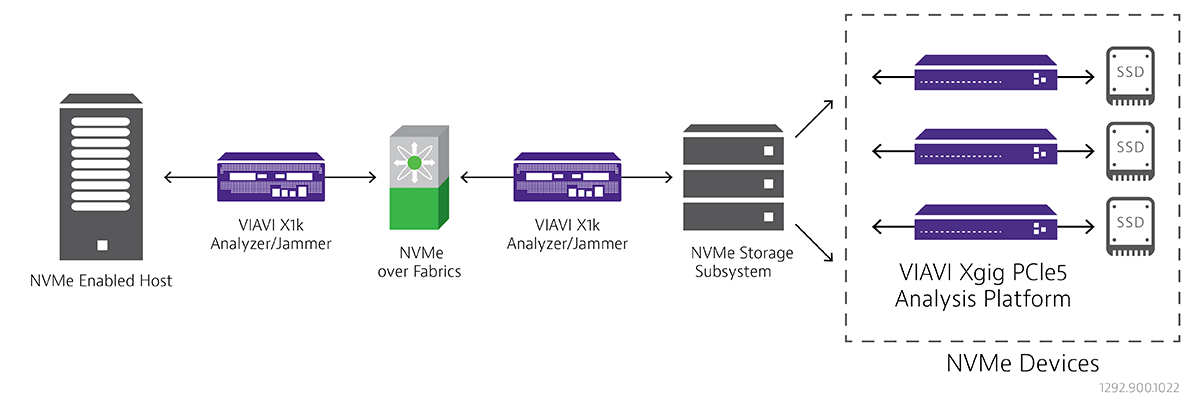

Mit der Einführung von NVMe over Fabrics (NVMe-oF) haben sich die Anforderungen an das Testen von PCIe weiter erhöht, da sich die Entfernung zwischen dem NVMe-Speichergerät und dem Host vergrößert, gleichzeitig aber eine zusätzliche Latenz von maximal 10 µs eingefügt werden darf. Obgleich die NVMe-oF-Spezifikation der ursprünglichen Leistungsbeschreibung für NVMe sehr ähnelt, erhöhen die Vorgaben für den Transportmechanismus die Komplexität des Testablaufs. In diesem Fall wird empfohlen, sowohl am NVMe-kompatiblen Host als auch am NVMe-Gerät, also an beiden Leitungsenden, einen entsprechenden Analysator/Jammer für PCIe/Ethernet/Fibre Channel einzusetzen.

PCIe 4.0

Die im Oktober 2017 veröffentlichte Version PCIe 4.0 hat einige Verbesserungen, wie das Lane-Margining und eine kürzere Latenz eingeführt, um die höhere Datenrate und Bandbreite, die von jeder neuen Generation erwartet werden, zu gewährleisten. Erweiterte Tags und Credits sowie eine verbesserte I/O-Virtualisierung zählen zu den zusätzlichen Leistungssteigerungen von PCIe 4.0, die mit jeder folgenden Generation weiter optimiert werden. Die Einführung der 4. Generation stellt in vielerlei Hinsicht bessere Einblicke in PCIe-Testabläufe, die durch die höhere Datenrate und die resultierenden Anforderungen an die Einfügedämpfung und das Margining komplexer wurden, zur Verfügung. Solche Funktionen, wie die Überwachung des Verkehrsflusses, die Datenspeicherung und die Fehlererkennung, erfordern leistungsstärkere PCIe-Tester. Mit der 5. Generation und den nachfolgenden Versionen setzt sich dieser Trend unvermindert fort.

PCIe 5.0

Das im Mai 2019 veröffentlichte Release von PCIe 5.0 ist das Ergebnis eines schnelleren Entwicklungszyklus, der sich darauf konzentrierte, die Voraussetzungen für die Verdopplung der Datenrate und Bandbreite zu schaffen und gleichzeitig möglichst keine neuen Leistungsmerkmale oder wesentliche Änderungen an der Architektur einzuführen. Daher hat die 5. Generation den 128b/130b-Leitungscode, die NRZ-Signalisierung und die Jitter-Parameter der 4. Generation übernommen. Um die doppelte Datenrate zu erzielen, wurde beim elektrischen Design der Schwerpunkt auf Signalintegrität und Entzerrung gelegt. Aufgrund der sich daraus ergebenden Kombination aus I/O-Durchsatz und Leistung bietet sich PCIe 5.0 als praktische Alternative für 400G-Ethernet-Strecken und anspruchsvolle cloudbasierte Netzwerke an.

Neue Möglichkeiten durch neue PCIe-Tester

Seit dem Release der 1. Generation wurden vielfältige PCIe-Tester und Testsoftware-Anwendungen entwickelt, um den hohen Ansprüchen gerecht zu werden. Diese Tools sollten die Leistung exakt ermitteln, Störungen umgehend erkennen und Nutzungsbedingungen effektiv simulieren, sodass eine robuste und umfassende Analyse gewährleistet war. In diesem Zusammenhang haben sich neue und innovative Kombinationen aus Protokollanalysatoren und Jammern für solche komplexen Einsatzszenarien wie NVMe-oF als ideal erwiesen.

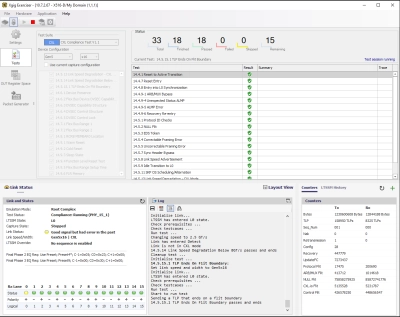

Analysatoren, die detaillierte Einblicke in die Verkehrsflüsse und die Leistungsparameter auf der Übertragungsstrecke vermitteln, erlauben nicht nur, das PCIe 5.0-Protokoll lückenlos zu überprüfen, sondern berücksichtigen auch die neuen, an die Übertragungsgeschwindigkeit und den Speicher gestellten Anforderungen. Jammer, die den aktuell übertragenen Verkehr manipulieren, gewährleisten einen robusten Grad der Simulation, der mit anderen Mitteln nicht erreichbar wäre. Die Software, auf der diese technisch hochentwickelten PCIe-Tester basieren, kombinieren deren Leistungspotenzial mit einer sich stetig weiterentwickelnden Benutzeroberfläche und mit Berichtsfunktionen, die den Techniker in die Lage versetzen, die PCIe-Tests intuitiv auszuführen.

Die PCI Special Interest Group (PCI-SIG) definiert die Spezifikationen und Konformitätsprüfungen, die das Zusammenwirken (Interoperabilität) der PCIe-Systeme garantieren sollen. Die Interessengruppe wurde 1992 gegründet und hat zurzeit mehr als 800 Mitgliedsunternehmen, die Produkte auf Grundlage der von der PCI-SIG veröffentlichten Vorgaben entwickeln. Diese Spezifikationen stehen den Unternehmen, Organisationen und Personen unter ihren Mitgliedern kostenfrei zur Verfügung. Weiterhin bietet die PCI-SIG auch Workshops zum Testen, für den technischen Support sowie zur Sicherung der Konformität von PCIe an. Die Konformitätsbibliothek der PCI-SIG umfasst eine ausführliche Liste der empfohlenen Hardware.

Als PCIe-Testkategorien sehen die Spezifikationen der PCI-SIG unter anderem die Überprüfung der elektrischen Parameter, der Konfiguration, der Protokolle der logischen Verbindung (Link) und der Transaktionsebene sowie des BIOS-Systems vor. Mit den steigenden Datenraten sind auch die Kanal-Topologien weitaus komplexer geworden. Zur Bewertung der PCIe-Verbindung wird daher empfohlen, den Verkehrsfluss zu simulieren, um die Leistung und Signalintegrität zu optimieren. Die Validierung des Protokolls auf der physikalischen Schicht (Bitübertragungsschicht) erlaubt zu prüfen, ob die Datenpakete zuverlässig übertragen werden. Der Test des Transaktionsprotokolls ermöglicht dem Techniker, kleinere Fehler (Debugging) zu überprüfen und zu beheben sowie die Einhaltung der PCI-SIG-Spezifikationen sicherzustellen.

Heute wird ein breites Spektrum unterschiedlicher Prüf- und Messtechnik für PCIe angeboten. Mit jeder neuen Generation dieser Technologie haben sich auch die entsprechenden Tester weiter entwickelt, um den immer anspruchsvolleren Anforderungen gerecht zu werden. Daher stehen immer wieder neue und umfassendere Lösungen zur Verfügung. Funktionsstarke Geräte renommierter Hersteller von Prüf- und Messtechnik für PCIe sind im Idealfall mobil, robust und umfassen selbstverständlich die Produktschulung und Zertifizierung. Angesichts der Abwärtskompatibilität der Schnittstelle müssen leistungsstarke PCIe-Tester die Interoperabilität mehrerer Größen und Versionen sowie ein schnelles Upgrades ermöglichen.

Jammer

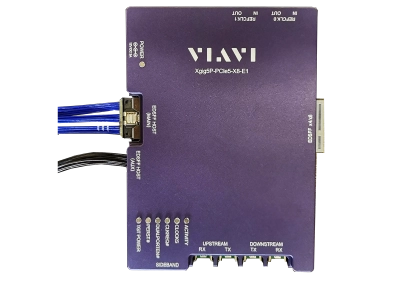

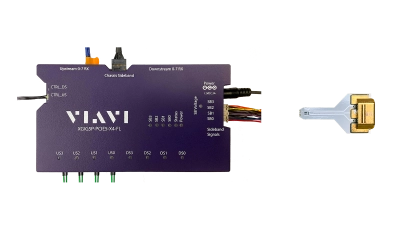

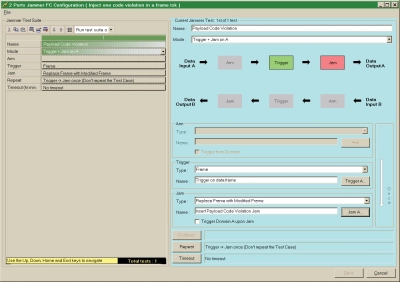

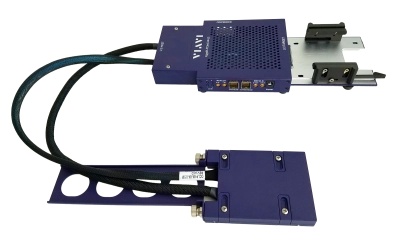

Ein Jammer kann den aktuell übertragenen Verkehr manipulieren, um Echtzeitfehler zu simulieren. Der Begriff „Jammer“ („Störsender“) geht bis auf die Mitte des 20. Jahrhunderts zurück und bezeichnete damals das vorsätzliche Stören der digitalen Kommunikationsverbindungen des Gegners. Bei PCIe-Tests fügt ein Jammer inline Fehler ein, um reale Einsatzbedingungen zu simulieren und die Testzyklen zu verkürzen. Hierfür nutzt der Jammer häufig vordefinierte, automatische Testskripts, um eine Vielzahl unterschiedlicher Fehler-Testszenarien zu erstellen.

Jammer, wie der Xgig sind äußerst intelligente und protokollorientierte Tester, die durch „bedingtes Stören“ die Kontrolle über den Testprozess behalten und eine lückenlose Testabdeckung sicherstellen. In Verbindung mit einem Protokollanalysator oder einem anderen PCIe-Tester erzeugt der Jammer an den Fehlereinfügungspunkten erkennbare Trigger. Durch das Einspeisen von Fehlern unter realen Bedingungen ist es möglich, die Reaktionsgeschwindigkeit und Effizienz des Fehlerbehebungsprozesses präzise zu bestimmen.

Analysatoren

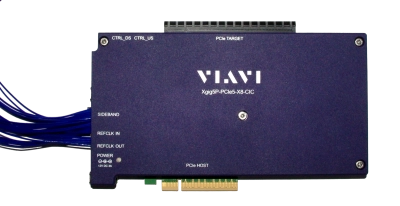

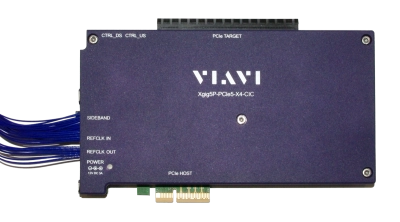

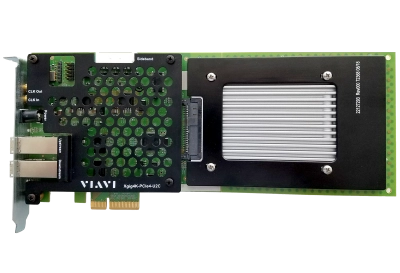

Der Protokollanalysator ist ein vielseitiger PCIe-Tester zum Ermitteln des Bus-Durchsatzes und der Leistung der Verbindungsstrecke sowie zum Überwachen und Aufzeichnen von Datenpaketen. Zusätzliche Trigger, die Meldung von Fehlern sowie Filterfunktionen beschleunigen die Identifizierung von Fehlern. Jamming-Funktionen können künstlich Latenzen und Übertragungswiederholungen erzeugen, um die Fehlererkennung zu trainieren.

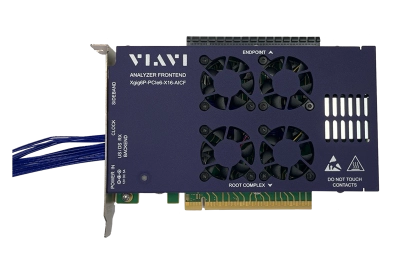

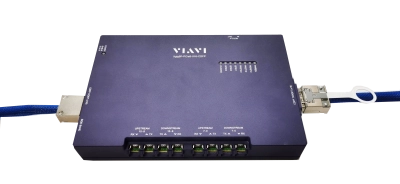

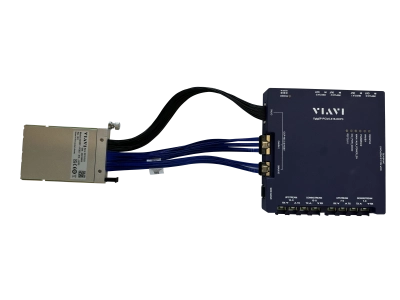

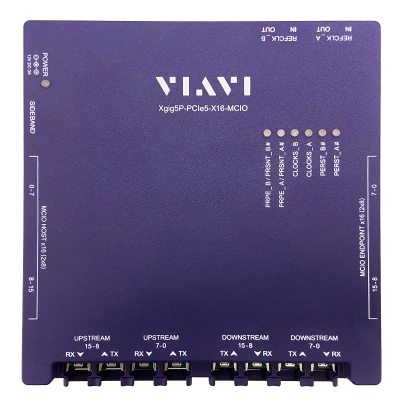

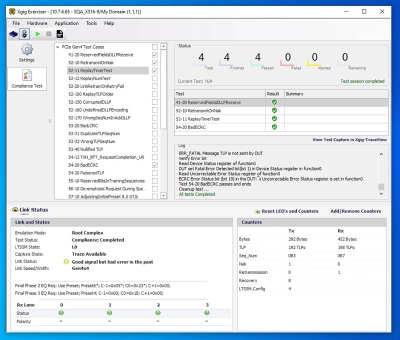

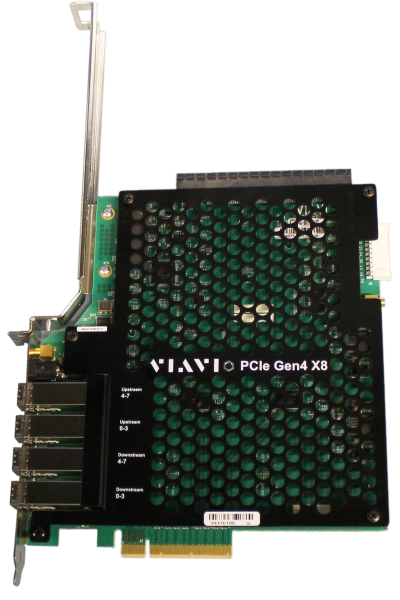

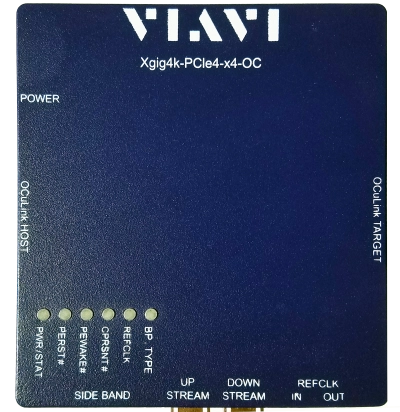

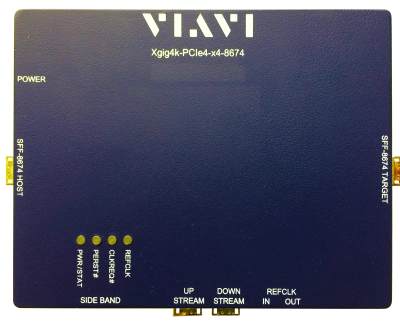

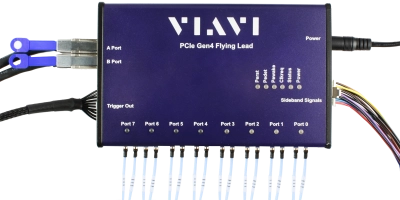

Hier sind leistungsstarke Analysatoren mit einer erweiterten Kurvenanalyse, mit Einblicken in den Verkehrsfluss sowie mit Speichersegmentierung von großem Wert. Der Xgig 4K16 Protocol Analyzer/Jammer ermöglicht die simultane Fehlereinfügung und Protokollanalyse. Zur Sicherung der Interoperabilität unterstützt dieser Tester unter anderem Lane-Breiten von x1, x2, x4, x8 und x16. Auf jeder Ebene des Protokollstapels werden die Benutzer über Alarme auf Fehler hingewiesen und eine erweiterte Speichernutzung erlaubt, mehrere Kurven gleichzeitig aufzuzeichnen.

Software

Die PCIe-Testsoftware ist die Grundlage, auf der sich die Technologie der Protokollanalysatoren und Jammer weiter entwickelt hat, um den steigenden Anforderungen an Datenrate, Funktionalität und Vielseitigkeit gerecht zu werden. Eine gut durchdachte Software kann helfen, sich wiederholende Funktionen zu automatisieren, anwendungsspezifische Routinen auf Grundlage der veröffentlichten Spezifikationen zu erstellen und mehrere Tester zu integrieren, um eine umfassende Funktionalität sicherzustellen. Moderne Berichtssoftware erlaubt, komplexe Datenanalysen zu vereinfachen und die Auswertung zu optimieren.

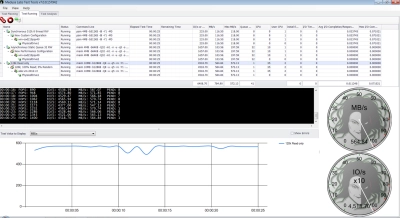

Die Software Xgig Expert, die zum Lieferumfang aller Xgig-Analysatoren gehört, stellt eine benutzerfreundliche Oberfläche zur Verfügung, die die Interpretation der Daten, das Debugging und die Fehlerdiagnose beschleunigt. Die Software durchsucht die aufgezeichneten Ereignisse effizient, um Mängel in der Leistung und Interoperabilität zu bewerten, Störungen auf der Bitübertragungsschicht, darunter Protokollverletzungen, zu identifizieren und die Ergebnisse auf Anforderung zu einem umfassenden Bericht zusammenzustellen. Zusätzliche Berichtssoftware ermöglicht das effiziente Datenmanagement, einschließlich der Filterung, Analyse und Präsentation der Daten.

Die Diagnose von PCIe-Störungen kann sich als recht schwierig erweisen. Glücklicherweise stellen viele leicht verfügbare PCIe-Tools auch herausragende Debugging- und Fehlerdiagnose-Funktionen zur Verfügung. Voraussetzungen für effektive PCIe-Tests und -Fehlerdiagnosen sind unter anderem aussagekräftige Einblicke in die Verkehrsflüsse und in die häufigsten Hardware-Störungen. Dazu zählen Probleme mit der Datenrate, wie Entzerrungsfehler, Verkehrsstörungen und Qualitätsprobleme nach der Fehlerbehebung. Fehlermeldungssoftware erlaubt, anwendungsspezifische Störungen zu finden und zu protokollieren sowie Fehlertypen, wie Zeitüberschreitungen und Übertragungsabbrüche, zu charakterisieren.

Ein Protokollanalysator, der mit einer analytischen Software ausgestattet ist, kann ein wichtiges und effektives Hilfsmittel zur PCIe-Fehlerdiagnose sein. Der Analysator erlaubt die mühelose Anzeige der Verkehrsflüsse und historischen Daten, die benötigt werden, um Störungen zu lokalisieren und zeitliche Abläufe darzustellen. Zudem besitzt der Analysator eine leistungsstarke Trigger-Funktion, die dem Techniker ermöglicht, auch extrem lange Sequenzen aufzuzeichnen, sowie Funktionen zum Filtern spezifischer Pakete, die die Untersuchung weiter optimieren. Die Protokollierung von Sequenzen in zeitlicher Reihenfolge erleichtert die Fehlerdiagnose, da Ereignisse direkt vor und nach dem gemeldeten Fehler detailliert angezeigt werden.

Seit dem Release der 1. Generation wurden immer wieder vielseitige PCIe-Tester und Testsoftware-Anwendungen entwickelt, um den hohen Ansprüchen gerecht zu werden. Diese Tools sollten die Leistung exakt ermitteln, Störungen umgehend erkennen und Nutzungsbedingungen effektiv simulieren, sodass eine robuste und umfassende Analyse gewährleistet war. In diesem Zusammenhang haben sich neue und innovative Kombinationen aus Protokollanalysatoren und Jammern für solche komplexen Einsatzszenarien wie NVMe-oF als ideal erwiesen.

Analysatoren, die aussagekräftige Einblicke in die Verkehrsflüsse sowie moderne Kurvenanalysen ermöglichen, werden auch nach dem Release von PCIe 5.0 ein unverzichtbares Hilfsmittel bleiben. Jammer, die den aktuell übertragenen Verkehr manipulieren, gewährleisten einen robusten Grad der Simulation, der mit anderen Mitteln nicht erreichbar wäre. Die Software, auf der diese technisch hochentwickelten PCIe-Tester basieren, kombinieren deren Leistungspotenzial mit einer sich stetig weiterentwickelnden Benutzeroberfläche und mit Berichtsfunktionen, die den Techniker in die Lage versetzen, die PCIe-Tests intuitiv auszuführen.

Die unmittelbare Zukunft von PCI Express hat mit der Veröffentlichung der 5. Generation im Jahr 2019 bereits Gestalt angenommen. Diese neue Revision verdoppelt, wie schon ihre Vorgänger, die verfügbare Bandbreite der 4. Generation. Neben dieser Leistungssteigerung unterscheidet sich die 5. Generation physisch durch kürzere Aussparungen (Keys). Zudem kommen auf der Leiterplatte bessere Materialien zum Einsatz. Zudem beliebt sie abwärtskompatibel zur 3. und 4. Generation. Daher sind für die Mainboards und Adapterkarten nicht sofort Upgrades erforderlich. Dass die Hardware-Designer und -Hersteller in ihren neuesten Angeboten weiter die PCIe-Schnittstelle berücksichtigen, stärkt deren Position als De-facto-Standard.

Rechenleistung und Speicher entwickeln sich jedoch in atemberaubendem Tempo weiter. Bisher ist es dem PCIe-Bus gelungen, mit diesem Tempo Schritt zu halten, aber der Abstand vergrößert sich. PCIe 6.0, das für 2021 erwartet wird, soll eine unglaubliche bidirektionale Bandbreite von 256 GB/s und Übertragungsraten von 64 GT/s zur Verfügung stellen, um dem Bedarf des maschinellen Lernens (ML), der künstlichen Intelligenz (KI) und anderer neuer, hochmoderner Anwendungen gerecht zu werden. In nicht allzu ferner Zukunft werden Leistungssteigerungen bei der Datenübertragung dazu führen, dass uns der heute so vertraute „Highspeed“-Bus wie ein Bummelzug erscheint. Vielleicht spielt keine andere Computer-Technologie eine so bedeutende Rolle wie der PCIe-Bus, wenn es darum geht, die Nachfrage nach einer immer höheren Geschwindigkeit und Bandbreite zu erfüllen. Daher stehen die Designer auf absehbare Zeit weiter unter großem Druck, neue Meilensteine im PCIe-Leistungspotenzial zu setzen.

Entdecken Sie PCIe mit VIAVI!

Sind Sie bereit, mit einem unserer Produkte und Lösungen für PCIe den nächsten Schritt zu gehen?

Füllen Sie eines der folgenden Formulare aus, um:

Literatur

Broschüren

Wir stehen Ihnen immer zur Seite

Bei uns erhalten Sie den Support, die Services, die umfassenden Schulungen und die Ressourcen, die Sie benötigen. Diese Leistungen tragen zur Maximierung Ihrer VIAVI Investitionen bei.

Fragen Sie einen Experten

Wenden Sie sich an uns, wenn Sie mehr Informationen oder ein Preisangebot wünschen. Bei uns finden Sie die Experten, die alle Ihre Fragen beantworten können.